## Adjustable Voltage Monitor

#### **General Description**

The ET3895 low power voltage detector provides monitoring of battery, power-supply, and regulated system voltages. The devices is a very small supervisory circuits that monitor voltages greater than 500mV with a 0.25% (typical) threshold accuracy and offer adjustable delay time using external capacitors.

The ET3895 also has a logic enable pin EN to power on and off the output. when the input voltage pin (IN) rises above the threshold, and the EN pin is high, then the output pin OUT goes high after the capacitor-adjustable delay time. When IN falls below the threshold or EN is low, then OUT goes low.

The ET3895 is available in ultra-small  $\mu$ DFN6 package and is fully specified the temperature range of T<sub>A</sub> = -40°C to 85°C.

#### **Features**

- Adjustable Threshold Down to 500mV

- Operate from V<sub>CC</sub> of 1.7V to 6.5V

- Threshold Accuracy: 1% Over Temperature

- Capacitor-Adjustable Delay Time

- Low Quiescent Current is 6μA Typical

- External Enable Input

- Temperature Range from -40°C to 85°C

- Package Information:

| Part No. | Package                  | MSL     |

|----------|--------------------------|---------|

| ET3895   | μDFN6(1.45 mm × 1.00 mm) | Level 1 |

#### **Application**

- Automotive

- DSPs, Microcontrollers and Microprocessors

- Notebook and Desktop Computers

- PDAs and Handheld Products

- Portable and Battery-Powered Products

- Medical Equipment

- FPGAs and ASICs

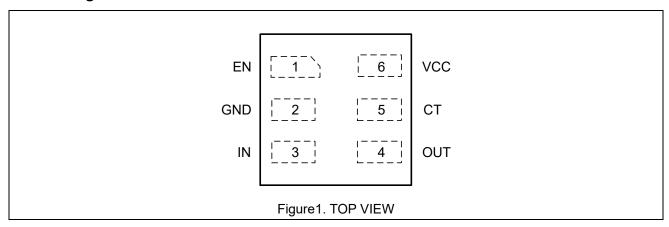

# Pin Configuration

### **Pin Function**

| Pin No. | Pin Name | I/O | Pin Function                                                                                                 |

|---------|----------|-----|--------------------------------------------------------------------------------------------------------------|

|         |          |     | Active high input. Driving EN low immediately makes OUT go low, drive EN                                     |

| 1       | EN       | I   | high to make OUT go high after the capacitor-adjustable delay time or 0.2µs                                  |

|         |          |     | (P version), independent of $V_{(IN)}$ . With $V_{(IN)}$ already above $V_{TH}$ .                            |

| 2       | GND      | ı   | Ground Pin.                                                                                                  |

|         |          |     | This pin is connected to the voltage that is monitored with the use of an                                    |

| 3       | INI      |     | external resistor. The output asserts after the capacitor-adjustable delay time                              |

| 3       | IN       | •   | when $V_{\text{(IN)}}$ rises above 0.5V and EN is asserted. The output deasserts after a                     |

|         |          |     | minimal propagation delay (16 $\mu$ s) when $V_{\text{(IN)}}$ falls below $V_{\text{TH}} - V_{\text{HYS}}$ . |

|         | 4 OUT O  |     | OUT is an push-pull output that is immediately driven low after $V_{\text{(IN)}}$ falls below                |

| 4       |          |     | (V <sub>TH</sub> – V <sub>HYS</sub> ) or EN input is low. OUT goes high after the capacitor- adjustable      |

|         |          |     | delay time when $V_{(IN)}$ is greater than $V_{TH}$ and the EN pin is high.                                  |

|         |          |     | Capacitor-adjustable delay. The CT pin offers a user-adjustable delay time.                                  |

| E       | СТ       |     | Connecting this pin to a ground referenced capacitor sets the delay time for                                 |

| 5       | 5 CT     |     | IN rising above CT 0.5V to OUT asserting (or EN asserting to OUT asserting).                                 |

|         |          |     | $t_{pd(r)}(s) = [C_{CT}(\mu F) \times 4] + 40\mu s$                                                          |

|         |          |     | Power supply input. Connect a 1.7V to 6.5V supply to VCC to power the                                        |

| 6       | VCC      | -   | device. It is good analog design practice to place a 0.1µF ceramic capacitor                                 |

|         |          |     | close to this pin.                                                                                           |

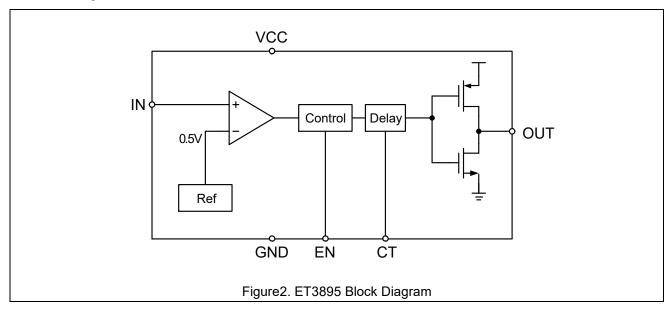

#### **Block Diagram**

### **Operation and Application Description**

The ET3895 is a ultra-small supervisory circuits. When the IN pin rises above 0.5V and the enable input is asserted (EN=high), the output asserts (OUT goes high) after the capacitor-adjustable delay time. The IN pin can be set to any voltage threshold above 0.5V using an external resistor divider. A broad range of output delay times and voltage thresholds can be supported, allowing these devices to be used in wide array of applications.

#### **Feature Description**

The ET3895 provide push-pull outputs. The logic high level of the outputs is determined by the VCC pin voltage. With this configuration, pull-up resistors are not required and some board area can be saved. However, all the interface logic levels must be examined. All the OUT connections must be compatible with the VCC pin logic level.

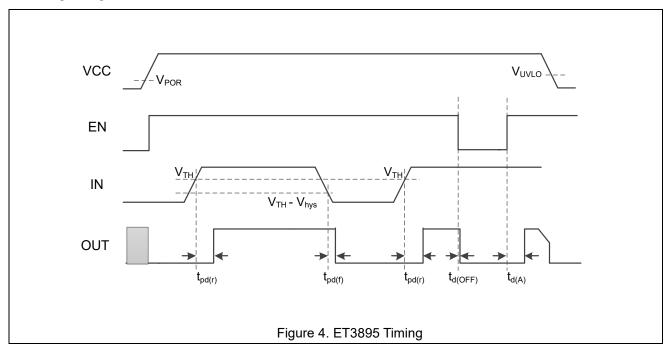

The OUT outputs are defined for a  $V_{CC}$  voltage higher than  $0.8V_{CC}$ . Table 1 are truth tables that describe how the outputs are asserted or de-asserted. When the conditions are met, the device changes state from de-asserted to asserted after a preconfigured delay time. However, the transitions from asserted to de-asserted are performed almost immediately with minimal propagation delay of 16 us (typical).

| Conditions |                               | Output     | Status                      |

|------------|-------------------------------|------------|-----------------------------|

| EN = Low   | EN = Low IN < V <sub>TH</sub> |            | Output not asserted         |

| EN = High  | IN < V <sub>TH</sub>          | OUT= Low   | Output not asserted         |

| EN = High  | IN > V <sub>TH</sub>          | OUT = High | Output asserted after delay |

| EN = Low   | IN > V <sub>TH</sub>          | OUT = Low  | Output not asserted         |

Table 1. ET3895 Truth Table

#### Input Pin (IN)

The IN input pin allows any system voltage above 0.5V to be monitored. If the voltage at the IN pin exceeds  $V_{TH}$ , and provided that the enable pin is asserted (EN=high), then the output is asserted after the capacitor-adjustable delay time elapses. When the voltage at the IN pin drops below ( $V_{TH}$  -  $V_{HYS}$ ), then the output is de-asserted. The comparator has a built-in hysteresis to ensure smooth output assertions and de-assertions. Although not required in most cases, for extremely noisy applications, it is good analog design practice to place a 1nF to 10nF bypass capacitor at the IN input in order to reduce sensitivity to transients and layout parasitics.

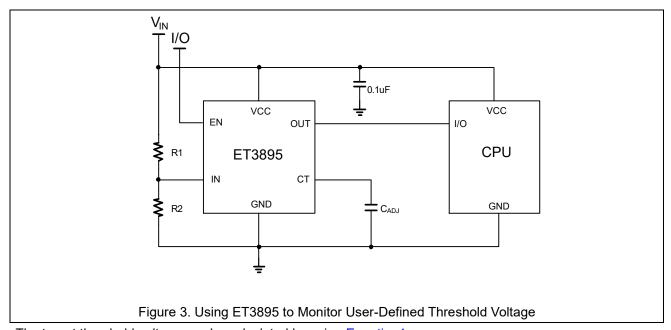

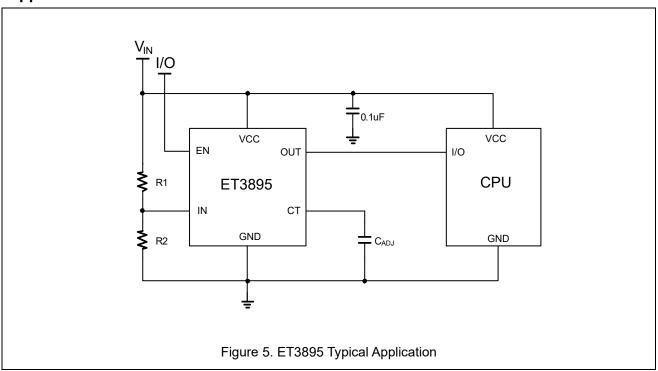

The ET3895 monitor the voltage at IN with the use of external resistor divider, as shown in Figure 3.

The target threshold voltage can be calculated by using Equation1:

$$V_{TARGET} = (1+R1/R2) \times 0.5 (V)$$

(1)

When the input voltage ( $V_{IN}$ ) is greater than  $V_{TARGET}$ , then the output is asserted, provided that the enable pin is asserted (EN=high). R1 and R2 can have high values (>100k $\Omega$ ) to minimize current consumption as a result of a low IN input current without adding significant error to the resistive divider.

#### **Enable Pin (EN)**

The enable input allows an external logic signal from other processors, logic circuits, and/or discrete sensors to turn on or turn off the output. Driving EN low forces OUT to go low. The 0.4V (maximum) low and 1.4V (minimum) high allow EN to be driven with a 1.5V or greater system supply.

ET3895 devices with  $V_{IN} > V_{TH}$ , driving EN high makes OUT go high after the capacitor-adjustable delay time.

#### **Output Pin (OUT)**

In a typical ET3895 application, the OUT outputs are connected to a reset/enable input of the processor (DSP, CPU, FPGA, ASIC, and so on) or connected to the enable input of a voltage regulator.

#### **Output Delay Time Pin (CT)**

To program a user-defined, adjustable delay time, an external capacitor must be connected between the CT pin and GND. If the CT pin is left open, there will be a delay of 40us. The adjustable delay time can be calculated through Equation 2:

$$tpd(r) (s) = [C_{CT}(\mu F) \times 4] + 40\mu s$$

(2)

The reset delay time is determined by the time it takes an on-chip, precision 310nA current source to charge the external capacitor to 1.24V. When IN >  $V_{TH}$  and with EN high, the internal current sources are enabled and begin to charge the external capacitors. When the CTn voltage on a capacitor reaches 1.24V, the corresponding OUT is asserted. Note that a low-leakage type capacitor (such as ceramic) should be used, and that stray capacitance around this pin may cause errors in the reset delay time.

The more precise of delay time can be calculated through Equation 3:

tpd(r) (s) =

$$[C_{CT} (\mu F) \times 4] *(310nA/I_{CT})*(V_{CT}/1.24) + 40 \mu s$$

(3)

IcT is the CT pin charge current;

V<sub>CT</sub> is the CT pin comparator threshold voltage.

#### **Immunity To IN Pin Voltage Transients**

The ET3895 is relatively immune to short negative transients on the IN pin. Sensitivity to transients depends on threshold overdrive.

#### **Device Functional Modes**

Normal Operation (V<sub>CC</sub> > V<sub>CC</sub>(min))

When the voltage on  $V_{CC}$  is greater than  $V_{CC}(min)$ , the output corresponds to the voltages on the  $V_{CC}$  and EN pins relative to  $V_{TH}$ .

Below Vcc (min) (VPOR < Vcc < VCC(min))</li>

When the voltage on  $V_{CC}$  is less than  $V_{CC}$ (min) but greater than the power-on reset voltage ( $V_{POR}$ ), the output is de-asserted (OUT is low).

Below Power-On Reset (V<sub>CC</sub> < V<sub>POR</sub>)

When the voltage on  $V_{CC}$  is lower than the power-on reset voltage ( $V_{POR}$ ), the output is undefined. Do not rely on the output for proper device function under this condition.

#### **PCB Layout Guide**

Follow these guidelines to lay out the printed-circuit-board (PCB) that is used for the ET3895.

Place the V<sub>CC</sub> decoupling capacitor close to the device.

Avoid using long traces for the  $V_{CC}$  supply node. The VCC capacitor ( $C_{VCC}$ ), along with parasitic inductance from the supply to the capacitor, can form an LC tank and create ringing with peak voltages above the maximum  $V_{CC}$  voltage.

#### **Power Supply Recommendations**

These devices are designed to operate from an input supply with a voltage range from 1.7V to 6.5V. Though not required, it is good analog design practice to place a 0.1uF ceramic capacitor close to the VCC pin.

#### Single-Rail Monitoring

The ET3895 can be used to monitor the supply rail for devices such as digital signal processors (DSPs), central processing units (CPUs), or field-programmable gate arrays (FPGAs). The downstream device is enabled by the ET3895 once the voltage on the IN pin  $(V_{IN})$  is above the threshold voltage  $(V_{TH})$  set by the resistor divider. The downstream device is disabled by the ET3895 when  $V_{IN}$  is falls below the threshold voltage minus the hysteresis voltage  $(V_{TH} - V_{HYS})$ .

#### **Design Requirements**

The ET3895 must drive the enable pin of devices using a logic-high signal to signify that the supply voltage is above the minimum operating voltage of the device.

#### **Detailed Design Procedure**

Select R1 and R2 so the voltage at IN  $(V_{IN})$  is above the positive-going threshold voltage  $(V_{TH})$  at the supply voltage required for proper device operation (that is, proper operation of the DSP, CPU, FPGA, and so on). Also, ensure that the current that flows from the supply voltage to ground through the resistor divider is at least 100 times larger than the input current  $(I_{IN})$ .

If an output delay time is required, connect a capacitor from CT to GND; see the Output Delay Time Pin (CT) section for more information. If no CT cap is connected, the delay time is 40us.

## **Absolute Maximum Ratings**

| Parameter                                     | Rating                        | Unit |

|-----------------------------------------------|-------------------------------|------|

| VCC,EN (push-pull) Voltage                    | -0.3 to 7.0                   | V    |

| CT ,OUT Voltage                               | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| OUT Current                                   | -10 to 10                     | mA   |

| Power Dissipation                             | 200                           | mW   |

| Package Thermal Resistance (θ <sub>JA</sub> ) | 250                           | °C/W |

| Operating Junction Temperature                | -40 to 150                    | °C   |

| Storage Temperature                           | -65 to 150                    | °C   |

# **Recommended Operating Conditions**

| Characteristic       | Symbol          | Min    | Max | Unit |

|----------------------|-----------------|--------|-----|------|

| Input supply voltage | Vcc             | 1.65   | 6.5 | V    |

| EN pin voltage       | V <sub>EN</sub> | 0      | 6.5 | V    |

| IN pin voltage       | V <sub>IN</sub> | 0      | 6.5 | V    |

| OUT pin voltage      | Vouт            | 0      | Vcc | V    |

| OUT pin current      | Іоит            | 0.0003 | 1   | mA   |

### **Electrical Characteristics**

$V_{\text{CC}}\text{=}1.7V$  to 6.5V,  $T_{\text{A}}\text{=}$  -40°C to +85°C, unless otherwise specified.

Typical values are at  $V_{CC}$  = 3.3V and  $T_A$  = +25°C

| Symbol            | Parameter                              | Test Conditions                            | Min                | Тур   | Max   | Unit |

|-------------------|----------------------------------------|--------------------------------------------|--------------------|-------|-------|------|

| Vcc               | Operating voltage range                | T <sub>A</sub> = 0°C to 85°C               | 1.65               |       | 6.5   | V    |

| V <sub>POR</sub>  | Power-on reset voltage                 | $V_{OL(MAX)} = 0.2V$ , $I_{OUT} = 15\mu A$ |                    |       | 1     | V    |

| 1                 | Supply current                         | V <sub>CC</sub> = 3.3V , no load           |                    | 5.5   | 11    |      |

| Icc               | (into VCC pin)                         | $V_{CC}$ = 6.5V , no load                  |                    | 6.5   | 11    | uA   |

| V <sub>тн</sub>   | Positive-going input threshold voltage | V <sub>IN</sub> rising                     | 0.495              | 0.500 | 0.505 | ٧    |

| V <sub>HYS</sub>  | Hysteresis voltage                     | V <sub>IN</sub> falling                    |                    | 3     |       | mV   |

| I <sub>IN</sub>   | Input current                          | V <sub>IN</sub> = 0V or V <sub>CC</sub>    | -15                |       | 15    | nA   |

| Іст               | CT pin charge current                  |                                            | 260                | 310   | 350   | nA   |

| Vст               | CT pin comparator threshold voltage    |                                            | 1.18               | 1.23  | 1.28  | V    |

| Rct               | CT pin pull-down resistance            |                                            |                    | 200   |       | Ω    |

| VIL               | EN Low-level input voltage             |                                            |                    |       | 0.4   | V    |

| V <sub>IH</sub>   | EN High-level input voltage            |                                            | 1.4                |       |       | V    |

| V <sub>UVLO</sub> | Under-voltage Lockout                  | V <sub>CC</sub> falling                    | 1.3                |       | 1.7   | V    |

| I <sub>LEAK</sub> | Leakage current                        | EN= GND                                    | -100               |       | 100   | nA   |

| V <sub>z</sub> .  | Low-level                              | V <sub>CC</sub> ≥ 2.25V, Isink = 0.5mA     |                    |       | 0.3   | V    |

| Vol               | output voltage                         | V <sub>CC</sub> ≥ 4.5V, Isink = 1mA        |                    |       | 0.4   | V    |

| Vau               | High-level                             | V <sub>CC</sub> ≥ 2.25V, Isource = 0.5mA   | 0.8V <sub>CC</sub> |       |       | V    |

| Vон               | output voltage                         | V <sub>CC</sub> ≥ 4.5V, Isource = 1mA      | 0.8Vcc             |       |       | V    |

### **Timing Requirements**

$V_{\text{CC}}$ =1.7V to 6.5V,  $T_{\text{A}}$ = -40°C to +85°C, unless otherwise specified.

Typical values are at  $V_{CC}$  = 3.3V and  $T_A$  = +25°C

| Symbol              | Parameter                     | Test Conditions                                        | Min | Тур | Max | Unit |

|---------------------|-------------------------------|--------------------------------------------------------|-----|-----|-----|------|

| <b>+</b>            | IN (rising) to IN-OUT         | $V_{(IN)}$ rising, $C_{(CT)}$ =open                    |     | 40  |     | us   |

| t <sub>pd(r)</sub>  | propagation delay             | $V_{\text{(IN)}}$ rising, $C_{\text{(CT)}} = 0.047 uF$ |     | 190 |     | ms   |

| <b>t</b>            | IN (falling) to IN-OUT        | V <sub>(IN)</sub> falling                              |     | 16  |     |      |

| t <sub>pd(f)</sub>  | propagation delay             | V(IN) Talling                                          |     | 10  |     | us   |

| t <sub>star</sub>   | Start-up delay <sup>(1)</sup> |                                                        |     | 50  |     | us   |

| t <sub>w</sub>      | EN pin minimum pulse duration |                                                        | 1   |     |     | us   |

|                     | EN pin glitch rejection       |                                                        |     | 100 |     | ns   |

| t vorry             | EN to IN-OUT delay time       | EN de-asserted to output                               |     | 200 |     | ns   |

| t <sub>d(OFF)</sub> | (output disabled)             | de-asserted                                            |     | 200 |     | 110  |

|                     |                               | EN asserted to output                                  |     | 20  |     | us   |

| <b>+</b>            | ENLAS IN OUT delay times      | asserted delay , $C_{(CT)}$ = open                     |     |     |     | us   |

| t <sub>d(A)</sub>   | EN to IN-OUT delay time       | EN asserted to output                                  |     |     |     | me   |

|                     |                               | asserted delay, $C_{(CT)} = 0.047uF$                   |     | 190 |     | ms   |

#### Notes:

- 1. During power on,  $V_{CC}$  must exceed 1.7V for at least 50us (plus propagation delay time,  $t_{pd(r)}$ ) before output is in the correct state.

- 2. tpd(r) decreases with the increase of  $V_{CC}$ , the typical characteristics are shown in the following table 2:  $(T_A = +25^{\circ}C, C_{CT} = 0.1uF)$

| Vcc         | 1.7V  | 2V    | 2.5V  | 3V    | 3.5V  | 4V    | 4.5V  | 5V    | 5.5V  | 6V    | 6.5V  |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| $t_{pd(r)}$ | 407ms | 406ms | 405ms | 405ms | 405ms | 405ms | 404ms | 402ms | 397ms | 386ms | 370ms |

Table 2. ET3895  $t_{\text{pd(r)}} vs \ V_{\text{CC}}$

## **Timing Diagram**

## **Application Circuits**

10

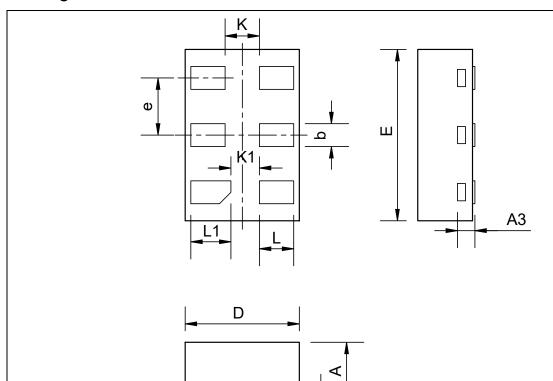

## Package Dimension

COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN     | NOM      | MAX   |  |  |

|--------|---------|----------|-------|--|--|

| Α      | 0.45    | 0.5      | 0.55  |  |  |

| A1     |         | 0.02REF  |       |  |  |

| A3     |         | 0.152REF |       |  |  |

| b      | 0.15    | 0.2      | 0.25  |  |  |

| D      | 0.9     | 1        | 1.1   |  |  |

| Е      | 1.35    | 1.45     | 1.55  |  |  |

| е      |         | 0.5BSC   |       |  |  |

| K      |         | 0.3REF   |       |  |  |

| K1     | 0.25REF |          |       |  |  |

| L      | 0.224   | 0.3      | 0.376 |  |  |

| L1     | 0.274   | 0.35     | 0.426 |  |  |

# **Revision History and Checking Table**

| Version | Date       | Revision Item                                                | Modifier              | Function & Spec<br>Checking | Package & Tape<br>Checking |

|---------|------------|--------------------------------------------------------------|-----------------------|-----------------------------|----------------------------|

| 1.0     | 2016-03-15 | Original Version                                             | Liu Yi Guo            | Zhu Jun Li                  | Zhu Jun Li                 |

| 1.1     | 2016-08-25 | Make dimension package with ±tolerance                       | Liu Yi Guo            | Zhu Jun Li                  | Zhu Jun Li                 |

| 1.2     | 2017-04-18 | Updated 'the EN pin is low' to 'the EN pin is high'          | Liu Yi Guo Zhu Jun Li |                             | Zhu Jun Li                 |

| 1.3     | 2017-04-19 | Add tpd(r) decreases with the increase of VCC and Equation 3 | Liu Yi Guo            | Zhu Jun Li                  | Zhu Jun Li                 |

| 1.4     | 2020-03-23 | Document check and formalize                                 | Shib                  | Liujy                       | Liujy                      |

| 1.5     | 2023-11-25 | Update Typeset                                               | Huyt                  | Huyt                        | Liujy                      |

|         |            |                                                              |                       |                             |                            |