## ET6416 - 16 bit I<sup>2</sup>C-bus/SMBus I/O Expander

#### General description

The ET6416 is a 16-bit general purpose I/O expander that provides remote I/O expansion for most micro-controller families via the I<sup>2</sup>C-bus interface.

ET6416 provides a simple solution for I/O port expansion, which can be realized with little interconnection. In addition to providing a set of flexible GPIO ports, it also supports the level conversion between different voltage devices, so that it can be flexibly applied in multi voltage mixed signal environment.

ET6416 has two supply voltage port: VDDI and VDDP, VDDI provides the power supply voltage for the interface of the main control terminal(micro-controller) and VDDP provides the power supply voltage for the core circuit and Port P.

ET6416 has four pairs of 8-bits registers: configuration register, input register, output register and polarity reversal register.

When power-on, all I/O ports are configured to input status. By configuring the I/O ports' configuration register, the system can determine the input and output status of each I/O port. Each input or output data is stored in the corresponding input or output register. The polarity of input registers can be flipped by configuring polarity reversal registers to save external logic gates.

When time-out or error operation occurs, the host can reset ET6416 by applying a low level on  $\overline{\text{RESET}}$  Port. When power on  $\overline{\text{RESET}}$ , all registers are in default state, and I<sup>2</sup>C BUS/SM BUS state machine is initialized.

When any input state is different from its corresponding input register state, the ET6416 open drain interrupt INT output is active to indicate to the host that the input state has changed.

The INT can be connected to the interrupt input of the micro-controller. By sending the interrupt signal, the microcontroller port is informed that there is data entering, instead of passing through I<sup>2</sup>C BUS.

The Port P output of ET6416 can provide 25mA perfusion current, which can directly drive LED.

The hardware address pin (ADDR) can be used to program and change the I<sup>2</sup>C BUS address.

#### **Features**

- I<sup>2</sup>C-BUS to parallel port expander

- Operating power supply voltage range of 1.65 V to 5.5 V

- Allows bidirectional voltage-level translation and GPIO expansion between:

- ◆ 1.8 V SCL/SDA and 1.8 V, 2.5 V, 3.3 V or 5 V Port P

- ◆ 2.5 V SCL/SDA and 1.8 V, 2.5 V, 3.3 V or 5 V Port P

- 3.3 V SCL/SDA and 1.8 V, 2.5 V, 3.3 V or 5 V Port P

- ◆ 5 V SCL/SDA and 1.8 V, 2.5 V, 3.3 V or 5 V Port P

- Low standby current consumption:

- ◆ 1.5uA typical at V<sub>DDP</sub> = 5 V

- ◆ 1.0uA typical at V<sub>DDP</sub> = 3.3 V

- Schmitt-trigger action allows slow input transition and better switching noise immunity at the SCL and SDA inputs

- ♦ V<sub>HYS</sub> = 0.18 V (typical) at 1.8 V

- ♦ V HYS = 0.25 V (typical) at 2.5 V

- ♦ V HYS = 0.33 V (typical) at 3.3 V

- $\bullet$  V HYS = 0.5 V (typical) at 5 V

- Active LOW reset input RESET

- Open-drain active LOW interrupt output INT

- 400 kHz Fast-mode I<sup>2</sup>C-BUS

- Input/Output configuration register

- Polarity Inversion register

- Internal power-on reset

- Power-up with all channels configured as inputs

- No glitch on power-up

- Noise filter on SCL/SDA inputs

- Outputs with 25 mA drive maximum capability for directly driving LEDs

- Latch-up performance exceeds 100 mA

- ESD protection exceeds

- ◆ ±2000 V Human-Body Model PASS

- ◆ ±1000 V Charged-Device Model PASS

- Package: VFBGA24

#### **Device Information**

| Part No. | Package | Size               |

|----------|---------|--------------------|

| ET6416   | VFBGA24 | 3mm × 3mm × 0.85mm |

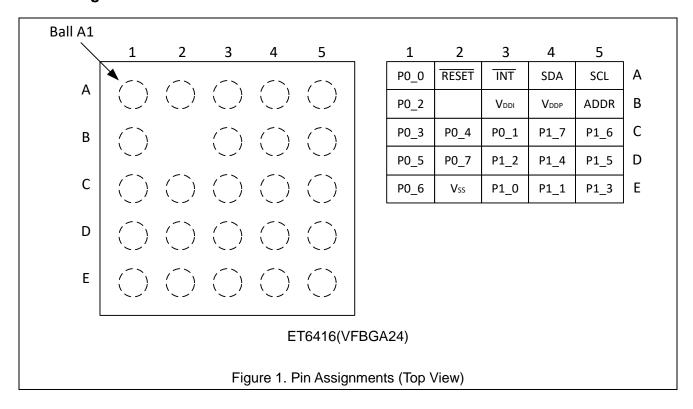

### **Pin Assignments**

#### Pin. Function

| Symbol    | Pin | Description                                                                                                          |

|-----------|-----|----------------------------------------------------------------------------------------------------------------------|

| ĪNT       | А3  | Interrupt output. Connect to V <sub>DDI</sub> (I <sup>2</sup> C-BUS) or V <sub>DDP</sub> through a pull-up resistor. |

| \/        | В3  | Supply voltage of I <sup>2</sup> C-bus. Connect directly to the VDD of the external I <sup>2</sup> C                 |

| $V_{DDI}$ | БЭ  | master. Provides voltage-level translation.                                                                          |

| RESET     | A2  | Active LOW reset input. Connect to V <sub>DD</sub> (I <sup>2</sup> C-BUS) through a pull-up resistor if              |

| RESET     | AZ  | no active connection is used.                                                                                        |

| P0_0      | A1  | Port 0 input/output 0.                                                                                               |

| P0_1      | C3  | Port 0 input/output 1.                                                                                               |

| P0_2      | B1  | Port 0 input/output 2.                                                                                               |

| P0_3      | C1  | Port 0 input/output 3.                                                                                               |

| P0_4      | C2  | Port 0 input/output 4.                                                                                               |

| P0_5      | D1  | Port 0 input/output 5.                                                                                               |

| P0_6      | E1  | Port 0 input/output 6.                                                                                               |

| P0_7      | D2  | Port 0 input/output 7.                                                                                               |

| Vss       | E2  | GND                                                                                                                  |

| P1_0      | E3  | Port 1 input/output 0.                                                                                               |

| P1_1      | E4  | Port 1 input/output 1.                                                                                               |

| P1_2      | D3  | Port 1 input/output 2.                                                                                               |

| P1_3      | E5  | Port 1 input/output 3.                                                                                               |

| P1_4      | D4  | Port 1 input/output 4.                                                                                               |

| Symbol           | Pin | Description                                                                                     |

|------------------|-----|-------------------------------------------------------------------------------------------------|

| P1_5             | D5  | Port 1 input/output 5.                                                                          |

| P1_6             | C5  | Port 1 input/output 6.                                                                          |

| P1_7             | C4  | Port 1 input/output 7.                                                                          |

| ADDR             | B5  | Address input. Connect directly to VDDP or ground.                                              |

| SCL              | A5  | Serial clock bus. Connect to V <sub>DD</sub> (I <sup>2</sup> C-bus) through a pull-up resistor. |

| SDA              | A4  | Serial data bus. Connect to V <sub>DD</sub> (I <sup>2</sup> C-bus) through a pull-up resistor.  |

| V <sub>DDP</sub> | B4  | Supply voltage of ET6416 for Port P.                                                            |

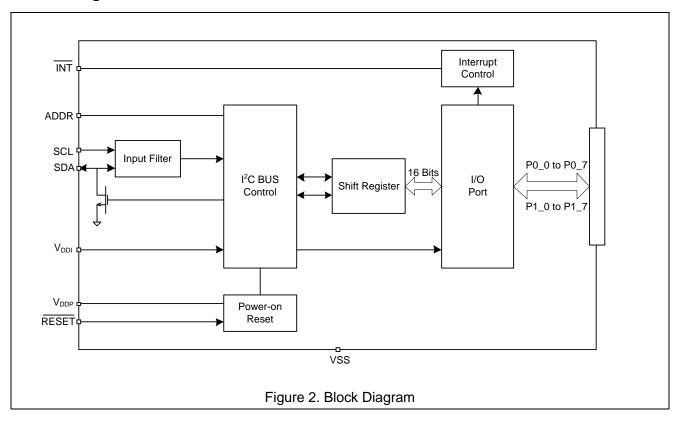

## **Block Diagram**

#### **Functions Description**

#### **Voltage Translation**

| V <sub>DDI</sub> (SDA and SCL) | V <sub>DDP</sub> (Port P) |

|--------------------------------|---------------------------|

| 1.8 V ~ 5.0V                   | 1.8 V ~ 5.0V              |

#### **BUS Transactions**

The ET6416 is an I<sup>2</sup>C-bus slave device. Data is exchanged between the master and ET6416 through write and read commands using I<sup>2</sup>C-bus. The two communication lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

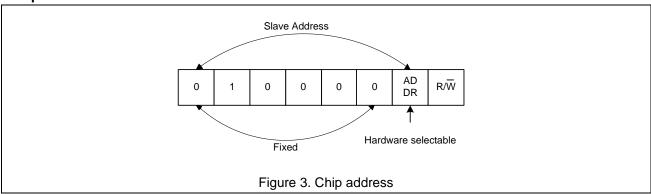

#### **Chip Address**

ADDR is the hardware address package pin and is held to either HIGH (logic 1) or LOW (logic 0) to assign one of the two possible slave addresses. The last bit of the slave address ( $R/\overline{W}$ ) defines the operation (read or write) to be performed. A HIGH (logic 1) selects a read operation, while a LOW (logic 0) selects a write operation.

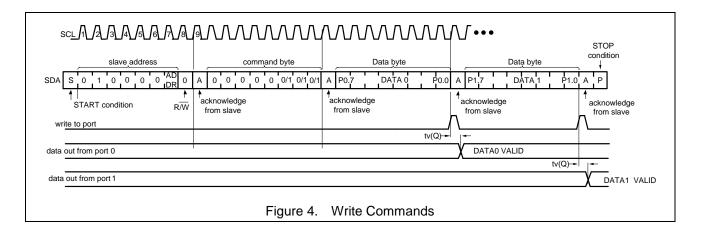

#### **Write Commands**

Data is transmitted to the ET6416 by sending the device address and setting the Least Significant Bit (LSB) to a logic '0'. The command byte is sent after the address and determines which register receives the data that follows the command byte.

The eight registers within the ET6416 are configured to operate as four register pairs. The four pairs are input Resisters, output Resisters, polarity inversion and configuration Registers. After sending data to one register, the next data byte is sent to the other register in the pair. For example, if the first byte is sent to Output Resisters1 (register 3), the next byte is stored in Output Resisters0 (register 2).

There is no limit on the number of data bytes sent in one write transmission. In this way, the host can continuously update a register pair independently of the other registers or the host can update a single register.

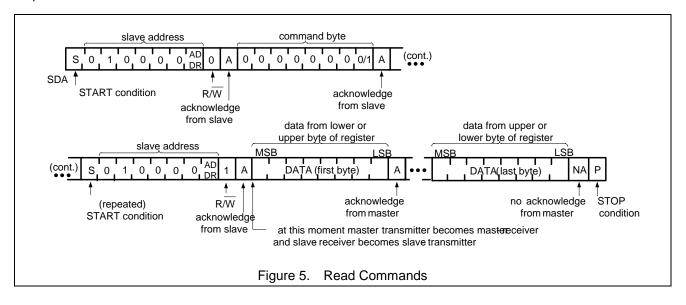

#### **Read Commands**

To read data from the ET6416, the bus master must first send the ET6416 address with the least significant bit set to a logic '0'. The command byte is sent after the address and determines which register is to be accessed.

After a restart, the device address is sent again, but this time the least significant bit is set to a logic '1'. Data from the register defined by the command byte is sent by the ET6416. Data is clocked into the register on the rising edge of the ACK clock pulse. After the first byte is read, additional bytes may be read, but the data now reflects the information in the other register in the pair. For example, if Input Resisters 1 is read, the next byte read is Input Resisters 0. There is no limit on the number of data bytes received in one read transmission, but on the final byte received the bus master must not acknowledge the data.

After a subsequent restart, the command byte contains the value of the next register to be read in the pair. For example, if Input Resisters 1 was read last before the restart, the register that is read after the restart is the Input Resisters 0.

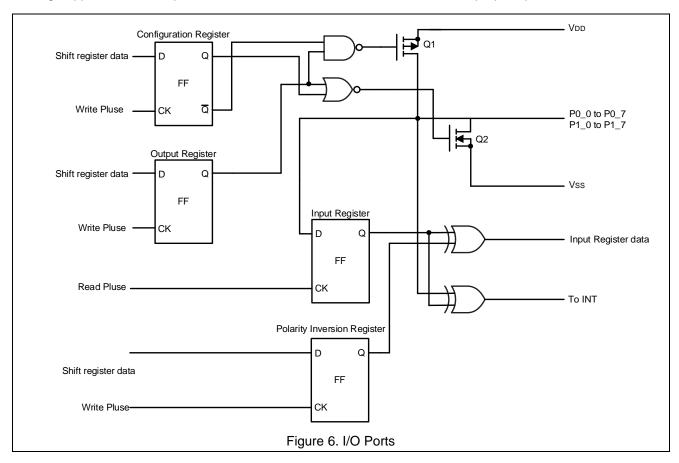

#### I/O Port

If the I/O is configured as an output, Q1 or Q2 is enabled, depending on the state of the Output port register. In this case, there are low-impedance paths between the I/O pin and either VDDP or VSS. The external

voltage applied to this I/O pin should not exceed the recommended levels for proper operation.

#### **Power-on Reset**

When power (from 0 V) is applied to VDDP, an internal power-on reset holds the ET6416 in a reset condition until VDDP has reached VPOR. At that time, the reset condition is released and the ET6416 registers and  $I^2C$ -bus/SMBus state machine initializes to their default states. After that, VDDP must be lowered to below VPOR and back up to the operating voltage for a power-reset cycle.

#### Reset Input (RESET)

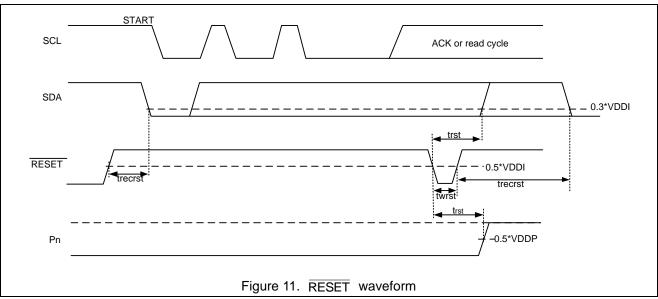

The  $\overline{\text{RESET}}$  input can be asserted to initialize the system while keeping the VDDP at its operating level. A reset can be accomplished by holding the  $\overline{\text{RESET}}$  pin LOW for a minimum of tw(rst). The ET6416 registers and I<sup>2</sup>C-bus/SMBus state machine are changed to their default state once  $\overline{\text{RESET}}$  is LOW (0). When  $\overline{\text{RESET}}$  is HIGH (1), the I/O levels at the P port can be changed externally or through the master. This input requires a pull-up resistor to VDDI(I<sup>2</sup>C-bus) if no active connection is used.

#### Interrupt Output (INT)

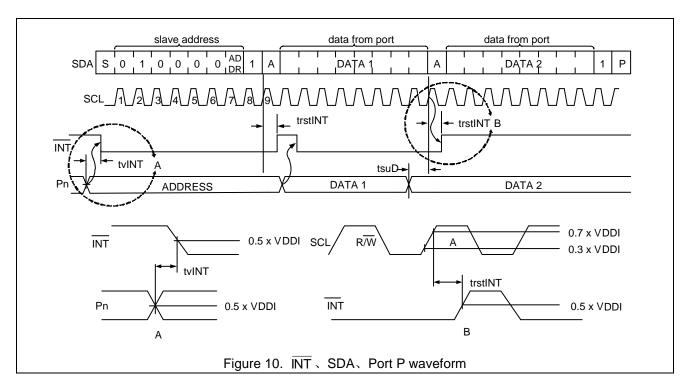

An interrupt is generated by any rising or falling edge of the port inputs in the Input mode. After time to V(INT), the signal  $\overline{INT}$  is valid. The interrupt is reset when data on the port changes back to the original value or when data is read from the port that generated the interrupt. Resetting occurs in the Read mode at the acknowledge (ACK) or not acknowledge (NACK) bit after the rising edge of the SCL signal. Interrupts that occur during the ACK or NACK clock pulse can be lost (or be very short) due to the resetting of the interrupt during this pulse. Any change of the I/Os after resetting is detected and is transmitted as  $\overline{INT}$ .

A pin configured as an output cannot cause an interrupt. Changing an I/O from an output to an input may cause a false interrupt to occur, if the state of the pin does not match the contents of the Input Port register.

The  $\overline{\text{INT}}$  output has an open-drain structure and requires pull-up resistor to VDDP or VDDI(I²C-bus) depending on the application.  $\overline{\text{INT}}$  should be connected to the voltage source of the device that requires the interrupt information.

#### Interface definition

| Duto                              | Bit    |      |      |      |      |      |      |        |  |

|-----------------------------------|--------|------|------|------|------|------|------|--------|--|

| Byte                              | 7(MSB) | 6    | 5    | 4    | 3    | 2    | 1    | 0(LSB) |  |

| I <sup>2</sup> C-BUSslave address | L      | Н    | L    | L    | L    | L    | ADDR | R/W̄   |  |

| 1/0 1-1-1                         | P0.7   | P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0   |  |

| I/O data bus                      | P1.7   | P1.6 | P1.5 | P1.4 | P1.3 | P1.2 | P1.1 | P1.0   |  |

#### Pointer register and Command byte

Following the successful acknowledgement of the address byte, the bus master sends a command byte, which is stored in the Pointer register in the ET6416. The lower three bits of this data byte state the operation (read or write) and the internal registers (Input, Output, Polarity Inversion, or Configuration) that will be affected. This register is write only.

While a new command has been sent, the register that was last addressed continues to be accessed by reads until a new command byte is sent.

| Pointer Register | Command byte | Pagistar                       | Protocol   | Default Value |

|------------------|--------------|--------------------------------|------------|---------------|

| Bits             | Command byte | Register                       | Protocoi   | Delault Value |

| 0000 0000        | 00h          | Input Registers 0              | Read only  | xxxx xxxx     |

| 0000 0001        | 01h          | Input Registers 1              | Read only  | xxxx xxxx     |

| 0000 0010        | 02h          | Output Registers 0             | Read/Write | 1111 1111     |

| 0000 0011        | 03h          | Output Registers 1             | Read/Write | 1111 1111     |

| 0000 0100        | 04h          | Polarity inversion Registers 0 | Read/Write | 0000 0000     |

| 0000 0101        | 05h          | Polarity inversion Registers 1 | Read/Write | 0000 0000     |

| 0000 0110        | 06h          | Configuration Registers 0      | Read/Write | 1111 1111     |

| 0000 0111        | 07h          | Configuration Registers 1      | Read/Write | 1111 1111     |

#### **Register descriptions**

| Register | Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|---------|------|------|------|------|------|------|------|------|

| 00h      | Symbol  | 10.7 | 10.6 | 10.5 | 10.4 | 10.3 | 10.2 | 10.1 | 10.0 |

| OOH      | Default | Χ    | X    | X    | X    | X    | Х    | Χ    | Х    |

| 01h      | Symbol  | l1.7 | I1.6 | I1.5 | l1.4 | I1.3 | I1.2 | I1.1 | I1.0 |

| UIII     | Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| 02h      | Symbol  | O0.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | O0.0 |

| 0211     | Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| 03h      | Symbol  | 01.7 | O1.6 | O1.5 | 01.4 | O1.3 | 01.2 | 01.1 | O1.0 |

| 0311     | Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| 04h      | Symbol  | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

| 0411     | Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 05h      | Symbol  | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| 05h      | Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| OCh      | Symbol  | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

| 06h      | Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| 07h      | Symbol  | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| 07h      | Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### Input Registers (00h, 01h)

The Input registers (registers 0 and 1) reflect the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by the Configuration register. The Input port registers are read only; writes to these registers have no effect.

The default value 'X' is determined by the externally applied logic level.

#### Output Registers (02h, 03h)

The Output registers (registers 2 and 3) shows the outgoing logic levels of the pins defined as outputs by the Configuration register. Bit values in these registers have no effect on pins defined as inputs. In turn, reads from these registers reflect the value that was written to these registers, not the actual pin value.

#### Polarity inversion Registers (04h, 05h)

The Polarity inversion registers (registers 4 and 5) allow polarity inversion of pins defined as inputs by the Configuration register. If a bit in these registers is set (written with '1'), the corresponding port pin's spolarity is inverted in the input register. If a bit in this register is cleared (written with a '0'), the corresponding port pin's polarity is retained.

#### Configuration Registers (06h, 07h)

The Configuration registers (registers 6 and 7) configure the direction of the I/O pins. If a bit in these registers is set to 1, the corresponding port pin is enabled as a high-impedance input. If a bit in these registers is cleared to 0, the corresponding port pin is enabled as an output.

*Note:* When the P port is suspended, configure it to the output state please.

### **Absolute Maximum Ratings**

| Symbol           | Parameter                                            | Conditions                                      | Min  | Max  | Unit |

|------------------|------------------------------------------------------|-------------------------------------------------|------|------|------|

| $V_{DDI}$        | I <sup>2</sup> C-bus supply voltage                  |                                                 | -0.5 | +6.5 | V    |

| $V_{DDP}$        | Supply voltage port P                                |                                                 | -0.5 | +6.5 | V    |

| VI               | Input voltage                                        |                                                 | -0.5 | +6.5 | V    |

| Vo               | Output voltage                                       |                                                 | -0.5 | +6.5 | V    |

| lıĸ              | Input clamping current                               | ADDR, $\overline{RESET}$ , SCL; $V_1 < 0V$      | -    | ±20  | mA   |

| Iok              | Output clamping current                              | ĪNT ; Vo < 0V                                   | -    | ±20  | mA   |

| 1                | Input/output                                         | P port; $V_0 < 0V$ or $V_0 > V_{DDP}$           | -    | ±20  | mA   |

| Іюк              | clamping current                                     | SDA; $V_0 < 0V$ or $V_0 > V_{DDI}$              | -    | ±20  | mA   |

| 1                | LOW lovel output ourrent                             | P port; $V_0 = 0V$ to $V_{DDP}$                 | -    | 50   | mA   |

| loL              | LOW-level output current                             | SDA, $\overline{INT}$ ; $V_O = 0V$ to $V_{DDI}$ | -    | 25   | mA   |

| Іон              | HIGH-level output current                            | P port; $V_0 = 0V$ to $V_{DDP}$                 | -    | 25   | mA   |

| I <sub>DD</sub>  | Supply current                                       | through Vss                                     | -    | 200  | mA   |

| I <sub>DDP</sub> | Supply current port P                                | through V <sub>DDP</sub>                        | -    | 160  | mA   |

| I <sub>DDI</sub> | I <sup>2</sup> C-bus supply current                  | through V <sub>DDI</sub>                        | -    | 10   | mA   |

| Tstg             | Storage temperature                                  |                                                 | -65  | +150 | °C   |

| Тлмах            | Maximum junction temperature                         |                                                 | -    | 150  | °C   |

| R <sub>θJA</sub> | Transient thermal impedance from junction to ambient | VFBGA24                                         |      | 171  | °C/W |

**Note:** Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

### **Recommended Operating Conditions**

| Symbol          | Parameter                                | Conditions            | Min                  | Max                  | Unit |

|-----------------|------------------------------------------|-----------------------|----------------------|----------------------|------|

| $V_{DDI}$       | I <sup>2</sup> C-bus supply voltage      |                       | 1.65                 | 5.5                  | V    |

| $V_{DDP}$       | Supply voltage port P                    |                       | 1.65                 | 5.5                  | V    |

| V               | V <sub>IH</sub> HIGH-level input voltage | SCL, SDA, RESET       | 0.7×V <sub>DDI</sub> | 5.5                  | V    |

| VIH             |                                          | ADDR, P1_7 to P0_0    | 0.7×V <sub>DDP</sub> | 5.5                  | V    |

| V/              | LOW level input voltage                  | SCL, SDA, RESET       | -0.5                 | 0.3×V <sub>DDI</sub> | V    |

| V <sub>IL</sub> | LOW-level input voltage                  | ADDR, P1_7 to P0_0    | -0.5                 | 0.3×V <sub>DDP</sub> | V    |

| Іон             | HIGH-level output current                | P1_7 to P0_0          | -                    | 10                   | mA   |

| loL             | LOW-level output current                 | P1_7 to P0_0          | -                    | 23                   | mA   |

| T <sub>A</sub>  | Ambient temperature                      | Operating in free air | -40                  | +85                  | °C   |

### **Electrical Characteristics**

#### **D.C. Characteristics**

$T_A = 25^{\circ}C$ ;  $V_{DDI} = 1.65V$  to 5.5V; (Unless otherwise specified.)

| Symbol           | Parameter              | Conditions                                                 | Min     | Тур | Max      | Unit |  |

|------------------|------------------------|------------------------------------------------------------|---------|-----|----------|------|--|

| Vıĸ              | Input clamping voltage | I <sub>I</sub> = -18mA                                     | -1.2    | -   | -        | V    |  |

| V <sub>POR</sub> | Power-on reset voltage | $V_I = V_{DDP}$ or $V_{SS}$ ; $I_O = 0mA$                  | -       | 1.1 | 1.4      | V    |  |

|                  |                        | P port                                                     |         |     |          |      |  |

|                  |                        | $I_{OH} = -8mA; V_{DDP} = 1.65V$                           | 1.2     | -   | -        | V    |  |

|                  |                        | $I_{OH} = -10 \text{mA}; V_{DDP} = 1.65 \text{V}$          | 1.1     | -   | -        | V    |  |

|                  | HIGH-level             | $I_{OH} = -8mA$ ; $V_{DDP} = 2.3V$                         | 1.8     | -   | -        | V    |  |

| $V_{OH}$         | output voltage         | $I_{OH} = -10 \text{mA}; V_{DDP} = 2.3 \text{V}$           | 1.7     | -   | -        | V    |  |

|                  | Output voltage         | $I_{OH} = -8mA; V_{DDP} = 3.0V$                            | 2.6     | -   | -        | V    |  |

|                  |                        | $I_{OH} = -10 \text{mA}; V_{DDP} = 3.0 \text{V}$           | 2.5     | -   | -        | V    |  |

|                  |                        | $I_{OH} = -8mA; V_{DDP} = 4.5V$                            | 4.1     | -   | -        | V    |  |

|                  |                        | $I_{OH} = -10 \text{mA}; V_{DDP} = 4.5 \text{V}$           | 4.0     | -   | -<br>1.4 | V    |  |

|                  |                        | P port; I <sub>OL</sub> =                                  | 8 mA    |     |          |      |  |

|                  | LOW-level              | $V_{DDP} = 1.65V$                                          | -       | -   | 0.45     | V    |  |

| $V_{OL}$         | output voltage         | $V_{DDP} = 2.3V$                                           | -       | -   | 0.25     | V    |  |

|                  | output voltage         | $V_{DDP} = 3.0V$                                           | -       | -   | 0.25     | V    |  |

|                  |                        | $V_{DDP} = 4.5V$                                           | -       | -   | 0.2      | V    |  |

|                  |                        | $V_{OL} = 0.4V$ ; $V_{DDP} = 1.65V$ to 5.5V                |         |     |          |      |  |

|                  |                        | SDA                                                        | 3       | -   | -        | mA   |  |

|                  |                        | ĪNT                                                        | 3       | 15  | -        | mA   |  |

|                  |                        | P port                                                     |         | 1   |          |      |  |

|                  |                        | $V_{OL} = 0.5V; V_{DDP} = 1.65V$                           | 8       | 10  | -        | mA   |  |

| I <sub>OL</sub>  | LOW-level              | $V_{OL} = 0.7V; V_{DDP} = 1.65V$                           | 10      | 13  | -        | mA   |  |

| IOL              | output current         | $V_{OL} = 0.5V; V_{DDP} = 2.3V$                            | 8       | 10  | -        | mA   |  |

|                  |                        | $V_{OL} = 0.7V; V_{DDP} = 2.3V$                            | 10      | 13  | -        | mA   |  |

|                  |                        | $V_{OL} = 0.5V; V_{DDP} = 3.0V$                            | 8       | 14  | -        | mA   |  |

|                  |                        | $V_{OL} = 0.7V; V_{DDP} = 3.0V$                            | 10      | 19  | -        | mA   |  |

|                  |                        | $V_{OL} = 0.5V; V_{DDP} = 4.5V$                            | 8       | 17  | -        | mA   |  |

|                  |                        | $V_{OL} = 0.7V; V_{DDP} = 4.5V$                            | 10      | 24  | -        | mA   |  |

|                  |                        | V <sub>DDP</sub> = 1.65V                                   | to 5.5V | _   |          | 1    |  |

| l <sub>l</sub>   | Input current          | SCL, SDA, $\overline{RESET}$ ; $V_I = V_{DDI}$ or $V_{SS}$ | -       | -   | ±1       | uA   |  |

|                  |                        | ADDR; $V_I = V_{DDP}$ or $V_{SS}$                          | -       | -   | ±1       | uA   |  |

| Iн               | HIGH-level             | P port; $V_I = V_{DDP}$ ;                                  | _       | _   | 1        | uA   |  |

| •1111            | input current          | $V_{DDP} = 1.65V \text{ to } 5.5V$                         |         |     |          | ۵, ۱ |  |

| I₁∟              | LOW-level              | P port; $V_1 = V_{SS}$ ;                                   | _       | _   | 1        | uA   |  |

| ·IL              | input current          | $V_{DDP} = 1.65V \text{ to } 5.5V$                         |         |     |          | G/ 1 |  |

| Symbol           | Parameter            | Conditions                                                                     | Min                   | Тур                 | Max                | Unit  |  |  |  |

|------------------|----------------------|--------------------------------------------------------------------------------|-----------------------|---------------------|--------------------|-------|--|--|--|

|                  |                      | I <sub>DDI</sub> + I <sub>DDP</sub> ; SDA, P port,                             | ADDR,                 | RESET;              |                    |       |  |  |  |

|                  |                      | $V_1$ on SDA and $\overline{RESET} = V_{DD1}$ or $V_{SS}$ ;                    |                       |                     |                    |       |  |  |  |

|                  |                      | $V_I$ on P port and ADDR = $V_{DDP}$ ;                                         |                       |                     |                    |       |  |  |  |

|                  |                      | $I_O = 0mA$ ; $I/O = inputs$                                                   | $F_{SCL} = 4$         | l00kHz              |                    |       |  |  |  |

|                  |                      | $V_{DDP} = 3.6V \text{ to } 5.5V$                                              | -                     | 10                  | 25                 | uA    |  |  |  |

|                  |                      | $V_{DDP} = 2.3V \text{ to } 3.6V$                                              | -                     | 6.5                 | 15                 | uA    |  |  |  |

|                  |                      | $V_{DDP} = 1.65V \text{ to } 2.3V$                                             | -                     | 4                   | 9                  | uA    |  |  |  |

|                  |                      | I <sub>DDI</sub> + I <sub>DDP</sub> ; SCL, SDA, P port, ADDR,                  | RESET;                | V <sub>I</sub> on S | CL, SD             | A and |  |  |  |

|                  | Cumple               | RESET =VDDI or VSS;VI on P                                                     | port and              | ADDR=               | V <sub>DDP</sub> ; |       |  |  |  |

| $I_{DD}$         | Supply               | $I_O = 0mA$ ; $I/O = input$                                                    | s; F <sub>SCL</sub> = | 0kHz                |                    |       |  |  |  |

|                  | current              | $V_{DDP} = 3.6V \text{ to } 5.5V$                                              | -                     | 1.5                 | 7                  | uA    |  |  |  |

|                  |                      | $V_{DDP} = 2.3V \text{ to } 3.6V$                                              | -                     | 1                   | 3.2                | uA    |  |  |  |

|                  |                      | V <sub>DDP</sub> = 1.65V to 2.3V                                               | -                     | 0.5                 | 1.7                | uA    |  |  |  |

|                  |                      | Active mode; IDDI + IDDP; P port, ADDR, RESET;                                 |                       |                     |                    |       |  |  |  |

|                  |                      | $V_I$ on $\overline{RESET} = V_{DDI}$ ; $V_I$ on P port and ADDR = $V_{DDP}$ ; |                       |                     |                    |       |  |  |  |

|                  |                      | $I_O = 0$ mA; I/O = inputs; $F_{SCL} = 400$ kHz, continuous register read      |                       |                     |                    |       |  |  |  |

|                  |                      | V <sub>DDP</sub> = 3.6V to 5.5V                                                | -                     | 60                  | 125                | uA    |  |  |  |

|                  |                      | $V_{DDP} = 2.3V \text{ to } 3.6V$                                              | -                     | 40                  | 75                 | uA    |  |  |  |

|                  |                      | V <sub>DDP</sub> = 1.65V to 2.3V                                               | -                     | 20                  | 45                 | uA    |  |  |  |

|                  |                      | SCL, SDA, RESET;                                                               |                       |                     |                    |       |  |  |  |

|                  |                      | one input at V <sub>DDI</sub> - 0.6V,                                          |                       |                     | 25                 |       |  |  |  |

|                  |                      | other inputs at V <sub>DDI</sub> or V <sub>SS</sub> ;                          | _                     | -                   | 25                 | uA    |  |  |  |

| A I              | Additional quiescent | $V_{DDP} = 1.65V \text{ to } 5.5V$                                             |                       |                     |                    |       |  |  |  |

| Δl <sub>DD</sub> | supply current       | P port, ADDR;                                                                  |                       |                     |                    |       |  |  |  |

|                  |                      | one input at V <sub>DDP</sub> - 0.6V,                                          |                       |                     | 80                 |       |  |  |  |

|                  |                      | other inputs at VDDP or Vss;                                                   | _                     | _                   | 00                 | uA    |  |  |  |

|                  |                      | V <sub>DDP</sub> = 1.65V to 5.5V                                               |                       |                     |                    |       |  |  |  |

| C.               | Input conscitones    | V <sub>I</sub> = V <sub>DDI</sub> or V <sub>SS</sub> ;                         |                       | 4.2                 | 7                  | ۲     |  |  |  |

| Cı               | Input capacitance    | $V_{DDP} = 1.65V \text{ to } 5.5V$                                             | -                     | 4.2                 | 7                  | pF    |  |  |  |

|                  |                      | $V_{IO} = V_{DDI} \text{ or } V_{SS}$ ;                                        | _                     | 4.5                 | 8                  | pF    |  |  |  |

| Cia              | Input/output         | $V_{DDP} = 1.65V \text{ to } 5.5V$                                             |                       | 4.5                 | 0                  | PΓ    |  |  |  |

| Сю               | capacitance          | $V_{IO} = V_{DDP} \text{ or } V_{SS}$ ;                                        |                       | 4.5                 | 8.5                | nE    |  |  |  |

|                  |                      | $V_{DDP} = 1.65V \text{ to } 5.5V$                                             |                       | 4.5                 | 0.0                | pF    |  |  |  |

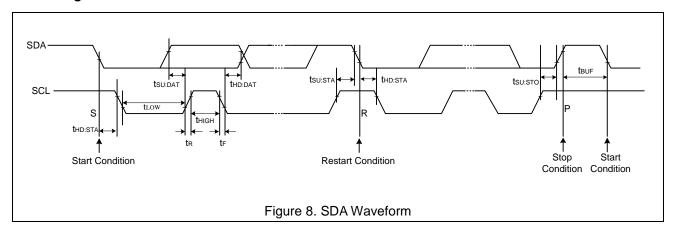

### A.C. Characteristics\*

$T_{\text{A}} = 25\,^{\circ}\text{C}; V_{\text{DDI}} = 1.65\text{V}$  to 5.5V; (Unless otherwise specified.)

| Symbol              | Parameter                                                         | Conditions                                  |     | rd-mode<br>·bus | Fast- | Unit |     |

|---------------------|-------------------------------------------------------------------|---------------------------------------------|-----|-----------------|-------|------|-----|

| <b>5</b> ,          |                                                                   |                                             | Min | Max             | Min   | Max  |     |

| fscL                | SCL clock frequency                                               |                                             | 0   | 100             | 0     | 400  | kHz |

| tнідн               | HIGH period of the SCL clock                                      |                                             | 4   | -               | 0.6   | -    | us  |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                       |                                             | 4.7 | -               | 1.3   | -    | us  |

| tsp                 | Pulse width of spikes that must be suppressed by the input filter |                                             | 0   | 50              | 0     | 50   | ns  |

| tsu;dat             | Data set-up time                                                  |                                             | 250 | -               | 100   | -    | ns  |

| thd;dat             | Data hold time                                                    |                                             | 0   | -               | 0     | -    | ns  |

| tr                  | Rise time of both SDA and SCL signals                             |                                             | -   | 1000            | -     | 300  | ns  |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                             |                                             |     | 300             | -     | 300  | ns  |

| tsu;sta             | Set-up time for a repeated START condition                        |                                             | 4.7 | -               | 0.6   | -    | us  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition                              |                                             | 4   | -               | 0.6   | -    | us  |

| tsu;sто             | Set-up time for STOP condition                                    |                                             | 4   | -               | 0.6   | -    | us  |

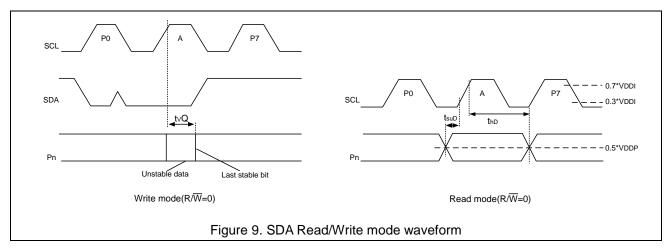

| t <sub>VD;DAT</sub> | Data valid time                                                   | SCL LOW to<br>SDA output valid              | -   | 3.45            | -     | 0.9  | us  |

| tvd;ack             | Data valid acknowledge time                                       | ACK signal from SCL<br>LOW to SDA (out) LOW | -   | 3.45            | ı     | 0.9  | us  |

| t <sub>wrst</sub>   | Reset pulse width                                                 |                                             | 30  | -               | 30    | -    | ns  |

| trecrst             | Reset recovery time                                               |                                             | 200 | -               | 200   | -    | ns  |

| t <sub>rst</sub>    | Reset time                                                        |                                             | 600 | -               | 600   | -    | ns  |

| t <sub>vINT</sub>   | Valid time on pin INT                                             | from P port to INT                          | -   | 1               | -     | 1    | us  |

| t <sub>rstINT</sub> | Reset time on pin INT                                             | from SCL to INT                             | -   | 1               | -     | 1    | us  |

| $t_{vQ}$            | Data output valid time                                            | from SCL to P port                          | -   | 400             | -     | 400  | ns  |

| t <sub>suD</sub>    | Data input set-up time                                            | from P port to SCL                          | 0   | -               | 0     | -    | ns  |

| $t_{hD}$            | Data input hold time                                              | from P port to SCL                          | 300 | -               | 300   | -    | ns  |

*Note\*:* Guaranteed by characterization. Not production tested.

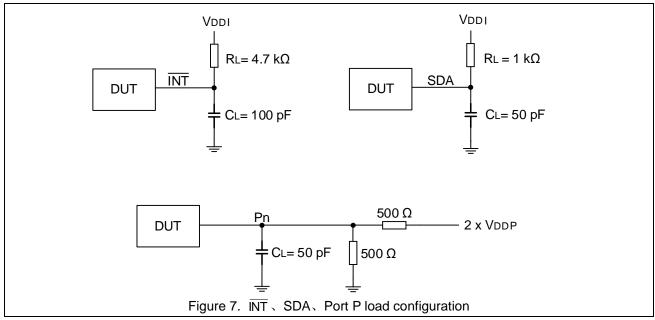

#### **Load Configuration**

*Note:* C<sub>L</sub> includes probe and clamp capacitance.

#### I<sup>2</sup>C Timing Waveform

¥ Rev 1.5

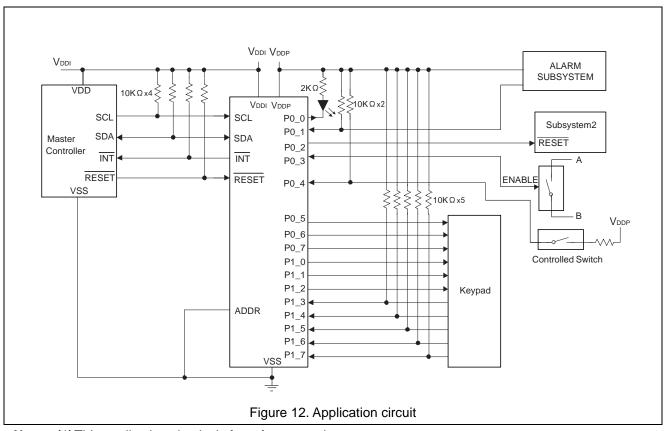

### **Application Circuits**

Note: (1) This application circuits is for reference only.

(2) When the P port is suspended, configure it to the output state please.

## **Package**

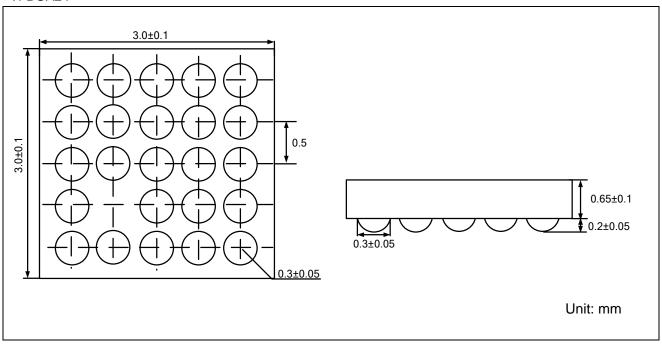

### VFBGA24

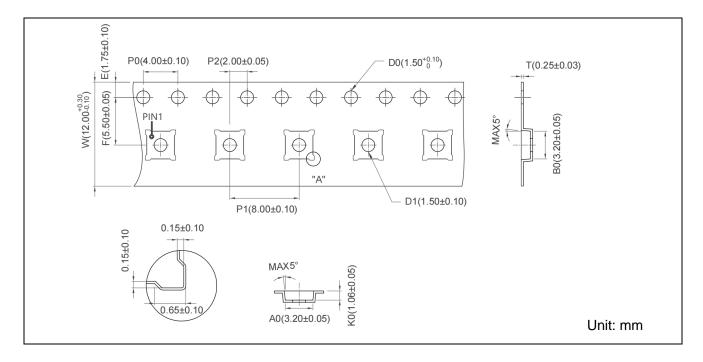

## **Tape Information**

I Rev 1.5

## **Revision History and Checking Table**

| Version | Date       | Revision Item                   | Modifier | Function & Spec<br>Checking | Package & Tape<br>Checking |

|---------|------------|---------------------------------|----------|-----------------------------|----------------------------|

| 0       | 2020-03-19 | Preliminary Version             | Shilj    | Shilj                       | Liujy                      |

| 1.0     | 2020-05-15 | Released Version                | Shilj    | Shilj                       | Liujy                      |

| 1.1     | 2020-10-13 | Add Marking                     | Shilj    | Shilj                       | Liujy                      |

| 1.2     | 2020-11-12 | Update Package<br>size of QFN24 | Shilj    | Shilj                       | Liujy                      |

| 1.3     | 2021-8-12  | Add note on page 6 and 15       | Shilj    | Shilj                       | Liujy                      |

| 1.4     | 2022-5-27  | Layout update                   | Shib     | Shilj                       | Liujy                      |

| 1.5     | 2023-1-22  | Update Typeset                  | Shib     | Shib                        | Liujy                      |