## 7-Channel LDO PMIC for Camera Applications

#### **General Description**

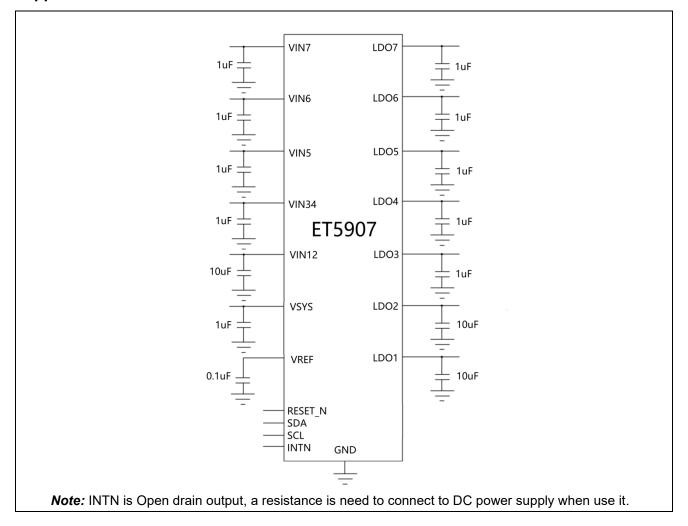

The ET5907 is CMOS-based low-dropout, low-power linear regulator. It's a 7-channel integrated LDOs for camera applications. Two channels offering max 1200mA with NMOS pass transistor, five channels offering max 400mA with PMOS pass transistor. ET5907 include 1000kHz high speed I2C interface, the function setting is flexible such as Under voltage lockout (UVLO), power sequence, output voltage, output discharge, current limit per channel. The chip enable control support EN pin control and I2C control.

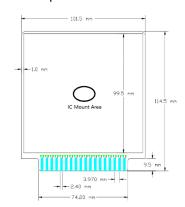

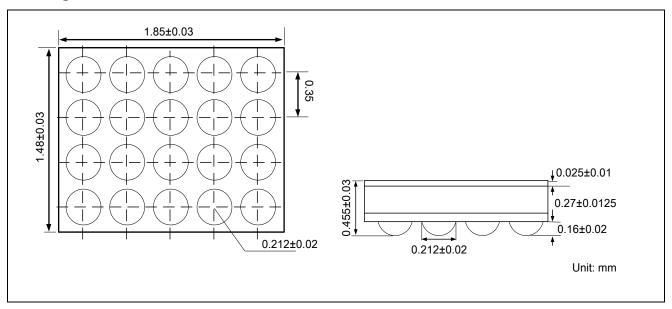

The ET5907 is available in 20-bump, 0.35 mm pitch, Wafer-Level Chip-Scale Package (WLCSP).

#### **Features**

- LDO1 and LDO2

- VIN12 input voltage range: 1.0V to 2.0V

- Programmable Output Voltage 0.8V to 1.8V in 6mV steps

- Max 1200mA Output Current Capability

- Ultra Low dropout: Typ.80mV at 800mA, 1.05V Output

- LDO3~LDO7

- VIN34/VIN5/VIN6/VIN7 input voltage range: 1.9 V to 5.5V

- Programmable Output Voltage 1.5V to 3.75V in 10mV steps

- Max 400mA Output Current Capability

- Less than 20uV(typ) Noise

- Ultra Low dropout: Typ. 85mV at 300mA, 2.8V Output

- Very Low input quiescent current of Typ. 150μA

- Operation guaranteed with battery voltage down to 2.7V

- Programmable Power Start-Up/Down Sequencing

- Built-in thermal Global Shutdown Protection (OTP)

- Built-in under Voltage Global Shutdown Protection(UVP)

- Built-in over current protection(OCP) and auto-discharging circuit

- Built-in under voltage lockout (UVLO)

- I<sup>2</sup>C serial control to program output voltage and features

- Package Information:

| Part No. | Package                | MSL     |  |

|----------|------------------------|---------|--|

| ET5907   | WLCSP-20 1.85mm×1.48mm | Level 1 |  |

#### **Applications**

- Constant-voltage power supply for battery-powered device

- Constant-voltage power supply for smartphones, tablets

- Constant-voltage power supply for cameras, DVRs, STB and camcorders

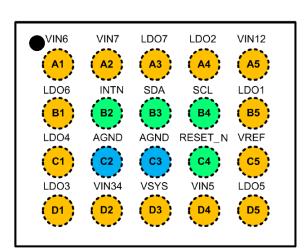

## **Pin Configuration**

TOP View (Bumps Down) WLCSP-20

#### **Pin Function**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                      |  |  |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A1      | VIN6     | Input power pin for LDO6.                                                                                                                                                         |  |  |

| A2      | VIN7     | Input power pin for LDO7.                                                                                                                                                         |  |  |

| A3      | LDO7     | LDO7 regulator output                                                                                                                                                             |  |  |

| A4      | LDO2     | LDO2 regulator output                                                                                                                                                             |  |  |

| A5      | VIN12    | Input power pin for LDO1 and LDO2.                                                                                                                                                |  |  |

| B1      | LDO6     | LDO6 regulator output                                                                                                                                                             |  |  |

| B2      | INTN     | Interface pin for interrupts. Open drain output.                                                                                                                                  |  |  |

| В3      | SDA      | I2C Data pin. Node should be tied high through a pull up resistor.                                                                                                                |  |  |

| B4      | SCL      | I2C Clock pin. Node should be tied high through a pull up resistor.                                                                                                               |  |  |

| B5      | LDO1     | LDO1 regulator output                                                                                                                                                             |  |  |

| C1      | LDO4     | LDO4 regulator output                                                                                                                                                             |  |  |

| C2      | AGND     | Ground pin.                                                                                                                                                                       |  |  |

| C3      | AGND     | Ground pin.                                                                                                                                                                       |  |  |

| C4      | RESET_N  | RESET_N pin is used to enable basic circuits necessary for controlling the PMIC. The RESET_N pin has an internal pull-down and should always be connected to a logic high or low. |  |  |

| C5      | VREF     | Reference bypass pin. If used, connect a 100nF capacitor between this pin and analog ground.                                                                                      |  |  |

| D1      | LDO3     | LDO3 regulator output                                                                                                                                                             |  |  |

| D2      | VIN34    | Input power pin for LDO3 and LDO4.                                                                                                                                                |  |  |

| D3      | VSYS     | System power pin. Route trace from system to this pin.                                                                                                                            |  |  |

| D4      | VIN5     | Input power pin for LDO5.                                                                                                                                                         |  |  |

| D5      | LDO5     | LDO5 regulator output                                                                                                                                                             |  |  |

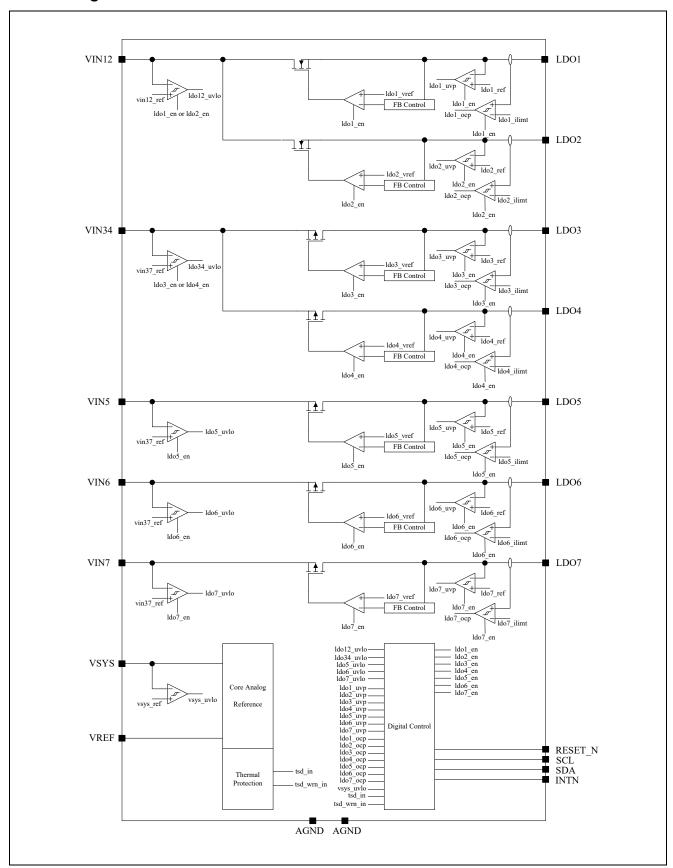

### **Block Diagram**

#### **Functional Description**

ET5907 has 7 LDO regulators. LDO1/2 are using NMOS pass transistor for output voltage regulation. The others LDOs are using PMOS pass transistor for output voltage regulation. The ET5907 LDO1 and LDO2 output voltages can be programmed via I2C from 0.8V to 1.8V in 6mV steps and LDO3-LDO7 can programmed from 1.5V to 3.75V in 10mV steps using the associated I2C registers. The voltage transition going from a lower to a higher voltage is a single step with transition time dependent on output current and output capacitance. The output current drives the voltage slew rate from higher to lower voltage transitions.

The device is in reset when the RESET\_N is low and will power up the device's main control circuits when RESET N is pulled high.

If LDOx\_EN bits are set to 1 prior to RESET\_N being asserted high, the LDOs will power up a short time after RESET\_N is pulled high. When the RESET\_N pin is pulled low, any interrupt bits in registers 0x15 to 0x17 will be cleared along with the status bits in 0x18 to 0x21. Additionally, all fault counters will reset to 0.

Enable of each LDO can be accomplished using I2C register LDOx\_EN bit in register 0x03 or the LDOs can be powered up/down sequentially using the Sequence State Machine, settable using the register bits in registers 0x0B to 0x0F. The device is also designed to support multiple start-up or shut-down sequences for multiple module loads.

The current limit and deglitch timer of each LDO can be programmed to optimize the LDO performance for the application. The device monitors each power input pin and each LDO output. If any of these below a threshold a status and interrupt bit are set.

#### **RESET\_N PIN and ENABLE BITS**

The tables below provide the states of the LDOs based on the combination of the enable pins and register bits.

| RESET_N | LDOX_SEQ | LDOX_EN | SEQ_CONTROL<br>Dependent | On/Off |

|---------|----------|---------|--------------------------|--------|

| Low     | 000      | 0       | No                       | Off    |

| High    | 000      | 0       | No                       | Off    |

| Low     | >000     | 0       | No                       | Off    |

| High    | >000     | 0       | Yes                      | CNTL   |

| Low     | 000      | 1       | No                       | Off    |

| High    | 000      | 1       | No                       | ON     |

| Low     | >000     | 1       | No                       | Off    |

| High    | >000     | 1       | Yes                      | CNTL   |

**Note**: CNTL indicates that the state of the output will be dependent on the setting of the seq\_ctrl[1:0] bits. When RESET N is high, seq\_ctrl[1:0]=2'b01 will enable any outputs based on their LDOX\_SEQ>000.

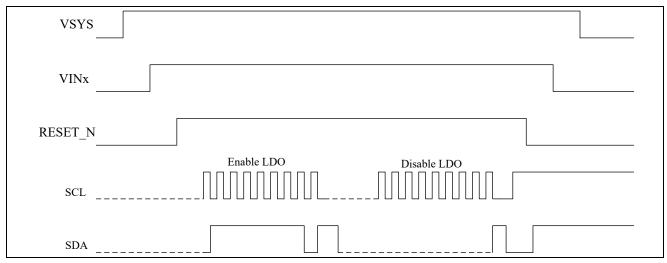

#### Power up/down sequence control

The recommended power on sequence of ET5907 is to power on VSYS first, then power on input power VINx, then set RESET\_N to high level, and then enable LDOx. The corresponding power off sequence is to turn off LDOx first, then set RESET\_N to low level, then power off input power VINx, and finally power off VSYS.

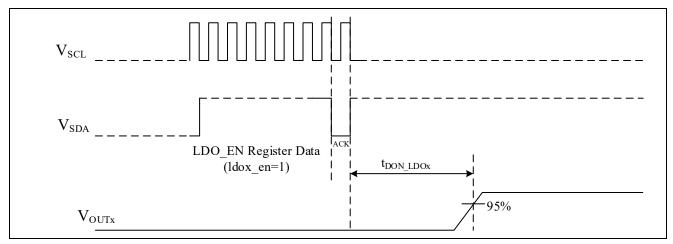

The ET5907 LDO's can be enabled two ways using the I2C register bits if RESET\_N is high.

- 1. Setting LDOX\_SEQ=000 in 0x0B(LDO12\_SEQ) or 0x0C(LDO34\_SEQ) or 0x0D(LDO56\_SEQ) or 0x0E(LDO7\_SEQ) and the LDOX\_EN assigned to the LDO in register 0x03, ENABLE to 1.

- 2. Setting LDOX\_SEQ>000 in registers 0x0B/C/D/E and then set seq\_ctrl[1:0]=2'b01 in the 0x0F, SEQ\_CTR register.

ET5907 LDOs have internal soft-start which limits the battery current to the setting LDOX\_ILIM in register 0x02. If an LDO output fails to reach 90% of the programmed voltage at start-up, a UVP fault is declared. See the output UVP section for description of LDO.

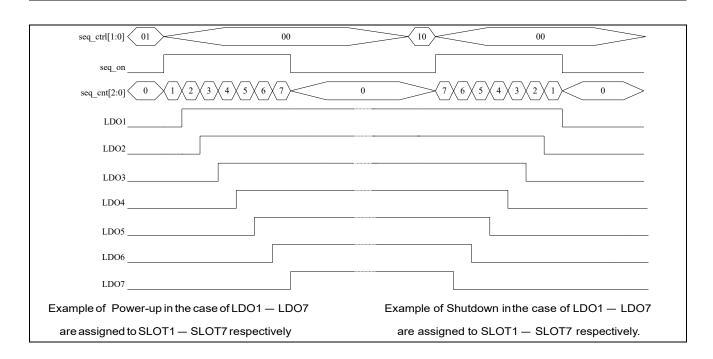

Power-up and shut down of each regulator can be controlled by an I2C register. It can be set at the registers Idox\_seq[2:0] (x=1 to 7) respectively. Idox\_en is an internal signal to enable one of regulators, if Idox\_seq[2:0] set to '000', that LDOX channel can be controlled directly by a bit specified in register LDO\_EN. LDOX\_VSET[7:0] can set output voltage of each channel.

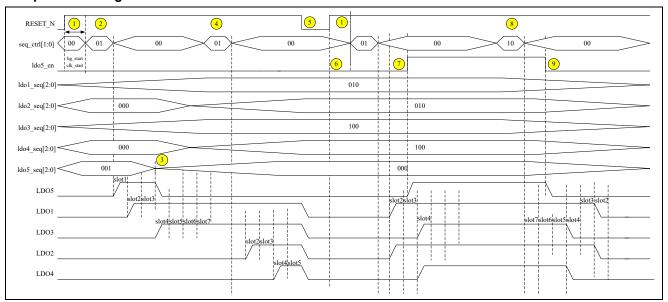

3. Automatic power up/down sequence control.

ET5907 has seven SLOTs to which each regulator can be assigned.

They are started by seq\_ctrl[1:0] signal. when seq\_ctrl[1:0] is set '01'. Internal counter seq\_cnt[2:0] starts increments from 0 ("000") to 7 ("111"). When seq\_ctrl[1:0] is set '10', seq\_cnt[2:0] decrements from 7 ("111") to 0 ("000"). Regulators assigned to one of SLOTs starts power-up or power-down.

The seq\_cnt[2:0] matches the SLOT number, when seq\_cnt[2:0]=000, it indicates that sequencing has completed or not started.

Internal logic signal seq\_on=1 indicates that sequencing is executing and somewhere between the start of slot 1 and the end of slot 7, seq\_on=0, it indicates that has completed or not started.

#### **Sequence Timing and Control**

#### State Description:

- 1. RESET\_N is asserted high and the band gap and internal clock are started. A minimum time of 100us needs to be allowed between RESET\_N being asserted high and seq\_ctrl[1:0] changed to 01 in order for the device to transition from shutdown to Sleep mode where the Bandgap and digital circuitry are enabled.

- 2. Upon seq\_ctrl[1:0] being set to 01, LDO5 is started in slot 1 (ldo5\_seq[2:0]=001). seq\_ctrl[1:0] bits are cleared immediately after the sequence is initiated. LDO1 and LDO3 are started in the associated slot given to their ldox\_seq value.

- 3. The ldo5\_seq[2:0] is set to 000, disabling the LDO.

- 4. Ido2\_seq[2:0] and Ido4\_seq[2:0] are set and a new sequence is started when seq\_ctrl[1:0] is set to 01 again. The state of any other LDO is not changed.

- 5. RESET N is pulled low and all LDOs are disabled.

- 6. RESET\_N is pulled high enabling the IC.

- 7. Ido5\_en is set to 1 and LDO5 is enable.

- 8. seq ctrl[1:0] is set to 10, starting a shutdown sequence

- 9. Asynchronous to the shutdown sequence LDO5 is disabled when Ido5\_en=0.

If an LDO faults during a start-up sequence, the other LDOs will still be started in their assigned time slot. The ldox\_seq[2:0] bits for the faulted LDO will remain set to the assigned slot. The system can then attempt to start the faulted LDO in another sequence by setting the seq\_ctrl[1:0] bits to 01 or by clearing the ldox\_seq[2:0] bits to 000 and then writing a "1" to the ldox\_en Enable bit.

#### **Shutdown**

To disable the ET5907 LDO(s), set the I2C register bit, Idox\_en assigned to the LDO in register 0x03 to 0 or if register, 0x0F, SEQ\_CTR bits [5:4], seq\_ctrl[1:0] is set to "10" and Idox\_seq[2:0]>000, the LDO(s) will be disabled in the Reserved order of time slot they are assigned. To do a global shutdown of all LDOs set the RESET\_N pin low.

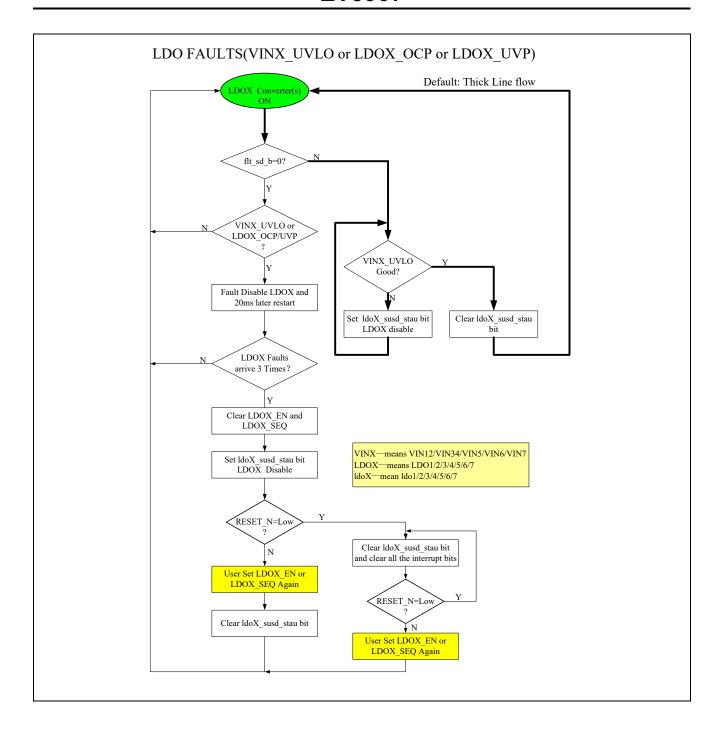

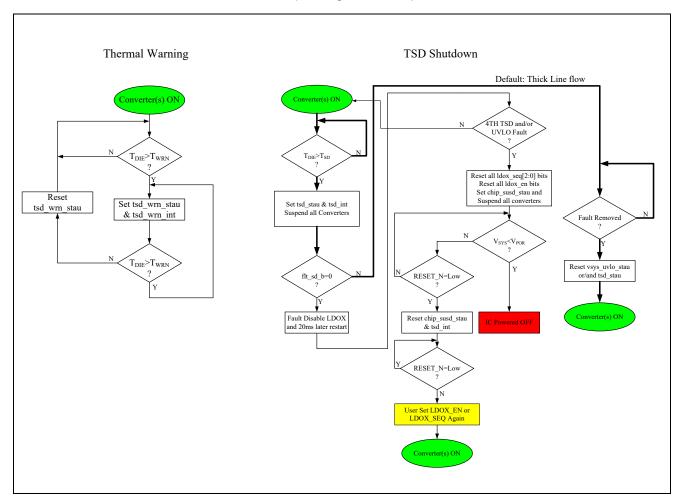

#### **Multiple Fault Shutdown**

To prevent repetitive starting and faulting of an LDO, detection of 3 failures will result in a complete shutdown of the LDO. If for instance LDO1 where to have a qualifying UVP condition and the LDO was disabled, LDO1 will be restarted 20ms later. If LDO1 where disable three times due to any faults (UVP, OCP or Short Circuit), LDO1 would be permanently shutdown until it is re-enabled by I2C commands. When LDO1 is shutdown under such a condition, the LDO1\_EN bit is set to 0 and the Ido1\_seq[2:0] is set to 000. This shutdown behavior applies to all of the ET5907 LDOs.

If UVP, OCP occurs when flt\_sd\_b is set to 1, the LDO(s) is not disabled and the fault counter is not incremented, but the interrupt and status bits indicate the fault occurred. flt\_sd\_b=1 doesn't prevent shutdown of LDOs when VIN12, VIN34, VIN5, VIN6 or VIN7 are in a UVLO condition, but the fault counter is not incremented.

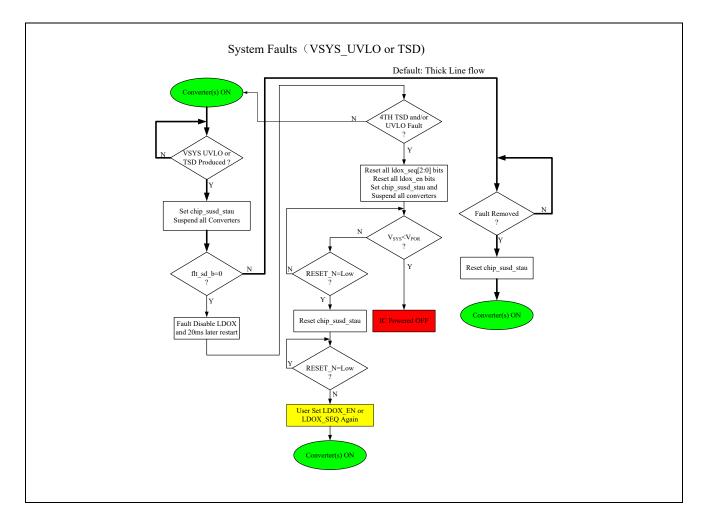

When flt\_sd\_b=0, if there are any combination of four VSYS\_UVLO and/or Thermal Shutdown faults(shutdown and after 20ms restart again for 4 times), the device will permanently shutdown and the chip\_susd\_stau bit will be set until RESET\_N has been set low and is asserted high again; When flt\_sd\_b=1, if there is VSYS\_UVLO or Thermal Shutdown faults, the device will shutdown and restart until the faults are released.

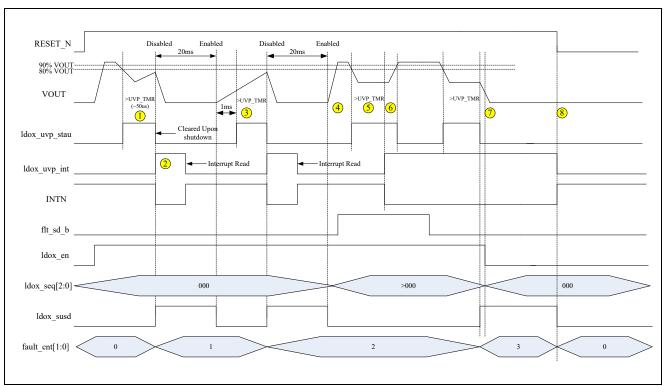

#### State Description:

- 1. A timer starts at the beginning of a UVP event and the UVP condition remains for the timer length(>50us), the converter is disabled for the first time.

- 2. The converter ldox\_uvp\_stau is set and 50us later the ldo\_uvp\_int bit is set and the INTN pin is pulled down. The converter is disabled and the ldo\_uvp\_stau bit is blanked, the ldox\_susd bit is set while the conveter is suspended until the next start. The fault\_cnt[1:0] is incremented upon shutdown.

- 3. The converter fails to reach UVP\_Rising(90% Vtarget) within 1ms of restart-up. Since the flt\_sd\_b=0, a second UVP failure is counted.

- 4. At the restart, the interrupt bit remains a 1until read. The Idox\_susd bit is reset by the restart action. The converter successfully reaches a voltage above UVP\_Rising within 1ms and runs. Meanwhile the flt\_sd\_b and Idox\_seg[2:0] are set to 1 and >000 respectively.

- 5. With flt\_sd\_b set to 1 when the fault occurs, the converter remains on, but the interrupt bit is set to one and INTN pin is pulled down. The ldox susd bit remains a "0" since the converter remains enabled.

- 6. The Ido\_uvp\_stau is set when the fault occurs, but clears when the converter is >90% of the target voltage.

- 7. When the converter is shutdown for the third time, the ldox\_en is set to 0; ldox\_seq is set to 000; The ldox\_uvp\_stau bit is set to 0. The fault\_cnt[1:0] keep three and ldox\_susd keep high level.

- 8. When RESET\_N is set low, the fault\_cnt[1:0] is cleared to 0 and Idox\_susd is cleared to 0. At the same time, Idox\_uvp\_int is cleared to 0. Another way to clear fault\_cnt[1:0] and Idox\_susd bits is reset the Idox\_en or Idox\_seg bit, and LDOx will restart again.

#### **UVLO Rising**

All LDOs use VSYS to power their analog and control circuitry. For proper operation the VSYS input is monitored for under voltage conditions. LDO1 and LDO2 use VIN12, LDO3 and LDO4 use VIN34, LDO5 uses VIN5, LDO6 uses VIN6 and LDO7 uses VIN7 to power their outputs.

If VSYS is greater than the POR threshold (~2.0V), but did not reach VSYS\_UVLO\_RISE when RESET\_EN is high, a UVLO interrupt vsys\_uvlo\_int bit and the status bit sys\_uvlo\_stau are set and the INTN pin is asserted low. When the LDO(s) are commanded to start or are running when VSYS falls below the UVLO threshold, but above VPOR, a re-start of the LDO(s) will be attempted again for the longer of 20ms (flt\_sd\_b=0) or when the VSYS rises above the VSYS\_UVLO\_RISE threshold. While in this state, the chip\_susd\_stau bit is set. The status bit remains set to "1" only while VSYS>VSYS\_UVLO\_RISE. The Interrupt bit will be cleared when read.

LDO1 and LDO2 may temporarily start if one or both VIN12 and VSYS have not reached VIN12\_UVLO THRESHOLD RISING or VSYS\_UVLO\_RISE level respectively prior to the LDO being enabled. If VSYS is good, but VIN12 is not when LDO1 and/or LDO2 are enabled, the interrupt bit Ido12\_uvlo\_int and status bit, Ido12\_uvlo\_stau are set and the INTN pin will be pulled low. Additionally, Ido1\_susd and/or Ido2\_susd will be set to "1" the longer of 20ms(flt\_sd\_b=0) or until VIN12 is greater than VVIN12\_UVLO\_RISE. At which time the SUSD bits will be cleared and the LDO(s) started. The Ido12\_uvlo\_stau, status bit remains set as long as VIN12 < VIN UVLO\_RISE. Similarly UVLO for VSYS, the LDO will not be restarted for a minimum of 20ms

and until VIN12 is greater than VIN12\_UVLO\_RISE. When the set output is low and the input voltage is less than 1.0V, the state of VIN12\_UVLO should be ignored.

UVLO for LDO3 and LDO4 are identical to that described above for LDO1 and LDO2. The UVLO threshold for LDO3 and LDO4 are VVIN34\_UVLO\_RISE. Behavior for LDO5, LDO6 and LDO7 are similar relative to VIN5, VIN6 and VIN7 as that discussed for LDO1.

#### Notes:

- Status bits may not be reliable until VSYS has reached a level of ~2.0V (VPORmax).

- The power on speed of VSYS should be faster than 2.5v/ms, otherwise it will be interrupted due to UVLO.

#### **UVLO Falling**

If VSYS falls below its VSYS\_UVLO\_FALL, falling threshold while one or more of the LDOs are enabled, a UVLO interrupt in 0x17, vsys\_uvlo\_int is set and the INTN pin is pulled low. A status bit in register 0x1A, vsys\_uvlo\_stau is also set while the rail remains below the rising UVLO threshold. Likewise, if VIN12, VIN34, VIN5, VIN6 or VIN7 fall below their falling threshold while the respective LDO is enabled, the associated input TSD\_UVLO\_STAU register bits will be momentarily set, the bits in TSD\_UVLO\_INT will be set and the INTN pin is pulled low. Then the LDOs will be disabled, the status bit reset and the associated ldox\_susd bit in 0x1B, SUSD\_STAU set to indicate the supply has been suspended.

PMIC Operation in VSYS UVLO

| VSYS State                                                                                    | RESET_N | Results                                                                |  |  |

|-----------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------|--|--|

| VSYS < VPOR                                                                                   | Low     | Device in shutdown, I2C registers not reliable                         |  |  |

| VPOR <vsys<uvlo< td=""><td>Low</td><td>Band Gap off, I2C registers readable</td></vsys<uvlo<> | Low     | Band Gap off, I2C registers readable                                   |  |  |

|                                                                                               |         | Upon POR initialization, all registers set to their default values. If |  |  |

| VSYS > UVLO                                                                                   | Low     | programmed prior to system fault, registers retain value and begin a   |  |  |

|                                                                                               |         | start up after RESET_N is high                                         |  |  |

| VSYS < VPOR                                                                                   | High    | Device in shutdown, I2C registers not reliable                         |  |  |

| VPOR < VSYS                                                                                   | l liada | Bond Con on 190 varietore readable                                     |  |  |

| <uvlo< td=""><td>High</td><td>Band Gap on, I2C registers readable</td></uvlo<>                | High    | Band Gap on, I2C registers readable                                    |  |  |

| VSYS > UVLO                                                                                   | Lliah   | Registers retain value prior to system fault and do an automatic       |  |  |

| VSTS > UVLO                                                                                   | High    | restart upon RESET_N going high.                                       |  |  |

When an over-temperature or a VSYS UVLO event occurs, all ET5907 LDOs are disabled for a minimum of 20ms(flt\_sd\_b=0). For UVLO on the LDO inputs, the individual LDO's will be disabled for a minimum of 20ms(flt\_sd\_b=0) and until the voltage rises above UVLO\_VSYS\_RISE.

#### **Current Limit Protection**

For each channel, when output current of LDO output pin is higher than current limit threshold or the output pin is direct short to GND, the current limit protection will be triggered and clamp the output current at a predesigned level to prevent over-current and thermal damage. Set related bits to select Current limit threshold register.

The LDO output current is short-circuit protected and the short-circuit current level can be programmed using the settings in register 0x02, LDO\_ILIMT. When a short occurs(VLDO1/2<30%VSET, VLDO3~7<0.5V) on the

LDOx output, the current is automatically limited to the programmed current limit and Vout may drop, depending on the difference between the input and target output voltage. The resultant VOUT is the product of current limit setting in register 0x02 LDO\_ILIMT and the load impedance. When current limit is detected, the associated OCP status bit in 0x19, OCP\_STAU is set to "1", If the LDOx remains in current limit for 1ms(default value), an interrupt bit in register 0x16, OCP\_INT is generated and the INTN pin is pulled low. Then the LDOx is disabled, the status bit in 0x16 OCP\_STAU register is reset to 0 and the associated suspend bit in the 0x1B SUSD\_STAU register is set to "1".

The LDOx will attempt a restart 20ms later(flt\_sd\_b=0) and the associated suspend will be reset to "0". If the associated interrupt bit was not read while the output was suspended, the interrupt will remain a 1 after restart and INTN (if not masked) will remain low.

Note: The OCP deglitch timer can be programmed to one of four periods by setting Reg. 0x11, bits [2:1].

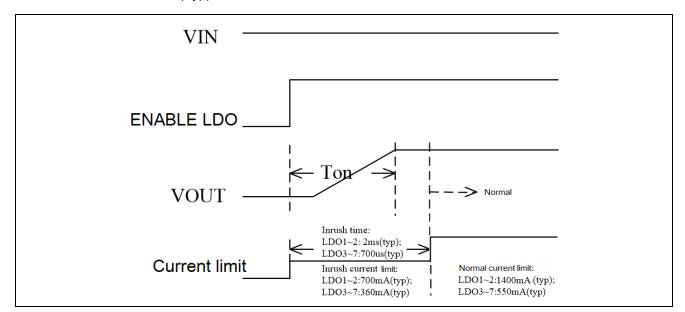

#### **Inrush Current Limit**

After enable the LDOs, the inrush current limit circuit is in operation, LDO1~2 inrush time is approximately 2ms, and LDO3~7 inrush time is approximately 700us. Therefore, the load current should be drawn after the output voltage reached the preset value.

If the load current is drawn during the start-up, it should be within the following values:

Register 0x02 is set to 0x7F:

lout1~2≤700mA on ldo1~2 (Typ);

Iout3~7≤360mA on Ido3~7(Typ).

Register 0x02 is set to 0x00:

Iout1~2≤600mA on Ido1~2 (Typ);

lout3 $\sim$ 7 $\leq$ 275mA on Ido3 $\sim$ 7(Typ).

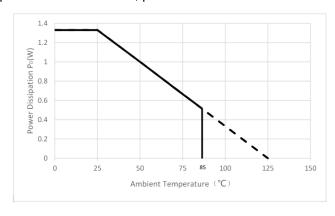

#### **Thermal Shutdown Protection**

When the die temperature rises to a nominal 125°C, a Thermal Warning interrupt occurs setting the tsd\_wrn\_int bit to "1" and INTN pin is pulled low. The tsd\_wrn\_stau register bit will be set to "1" and remain set until the die temperature drops to a nominal value of 100°C.

If the die temperature continues to rise above the thermal warning level, a Thermal Shutdown event is activated at a nominally 145°C. When the Thermal Shutdown level is reached, all power outputs are disabled without shutdown sequencing, but I2C communications remain. The device remains in thermal shutdown until the die temperature falls to approximately +120°C.

At the time a Thermal Shutdown detection occurs, the tsd\_int, interrupt bit is set and the INTN pin is pulled low to notify the system of the event. The tsd\_stau, register bit is also set and will remain set as long as the device is above TWRN°C. The C\_SUSD bit is set while the device is shutdown due to the overtemp condition.

After the die temperature has fallen below the TWRN threshold following a Thermal Shutdown event, the state of the I2C control registers will remain as they were prior to shutdown, the tsd\_wrn\_stau and tsd\_stau bits will clear and the device will return to the operating conditions prior to the thermal shutdown event.

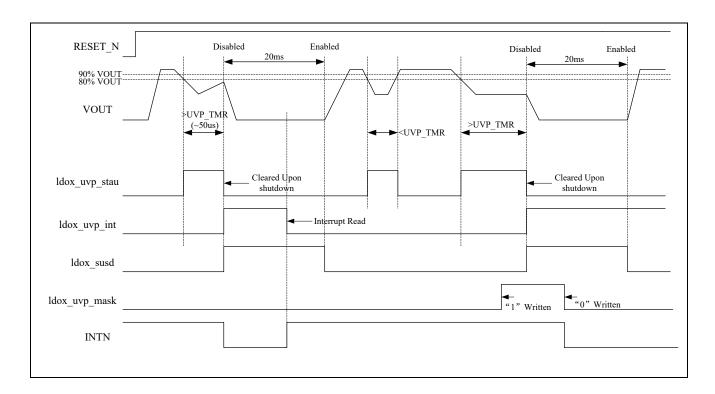

#### **Output UVP (Under Voltage Protection)**

If the LDO is enable and the output voltage falls approximately 20%(10% for LDO1/2) below the programmed voltage, the associated UVP Status bit in register 0x18, UVP\_STAU will be set to "1". If the fault persists for more than 50us the UVP Interrupt bit in register 0x15, UVP\_INT will be set to "1" and the INTN pin will be pulled low. The LDO will then be disabled, the associated Status bit set back to "0" and Suspend bit in 0x1B, SUSD\_STAU set to a "1". The interrupt bit will be cleared upon a read of the bit.

The LDO will be restarted 20ms (providing it is not the third fault) after it was shutdown by a UVP event and the suspend bit in SUSD\_STAU reset to "0". If the associated UVP interrupt bit is not read while the output was suspended, the interrupt (if not masked) will remain a "1" after restart and INTN will remain low.

In order to make the UVP of LDO 3 ~ 7 work normally, the input voltage of LDO should be greater than the output voltage, and the voltage of VSYS should be greater than the output voltage of LDO.

**Note:** For LDOx, if VSYS<VOUTx+1.1V(x=1~7), the output UVP interrupt output function for LDOx can not be used. And the corresponding mask UVP interrupt bit in LDOx\_MASK(0x1C) register should be set to 1(mask LDOx UVP interrupt output function) through I2C before enable LDOx.

**Recommended:** Set LDOx\_MASK(0x1C) to 0x7F before enable LDOx through I2C to disable all LDO UVP interrupt output function.

#### **UVP Timing**

The timing diagram below represents the general way each LDO's under-voltage circuitry behave. The names shown in the diagram are general descriptions.

In the first UVP detection case, the Idox\_uvp\_stau bit is set when the fault is detected and after a 50us wait period, the Idox\_uvp\_int bit is set and the INTN pin is pulled low. The LDO output is disabled, the Status bit is reset and then the associated Idox\_susd bit in SUSD\_STAU register is set. After 20ms(flt\_sd\_b=0) the LDO is restarted and the SUSD\_STAU bit is cleared. Shown in the graph is a read of the interrupt bit register before the 20ms expires. This clears the interrupt bit and the INTN pin is released and rises high.

In the second case, the output is not in the UVP condition for the qualifying time (UVP\_TMR) and ldox uvp stau bit returns to 0.

For the third case, the output falls for longer than UVP\_TMR and the interrupt bit is set, the LDO is disabled, the Status bit reset and the Idox\_susd, suspend bit is set. Since the interrupt is masked by Idox\_uvp\_mask, the INTN pin is not pulled low until the Mask bit is set back to "0". When the LDO is re-enabled after 20ms(flt\_sd\_b=0), the Idox\_uvp\_int remains a "1" as the register bit was not read.

#### **Auto Discharging**

For each channel, when shut down the output, the Auto-Discharging circuit will be turned on to discharge the electric charge on output capacitor, and decrease the voltage of output pin in very short time. The Auto-Discharging function is optional. Set related bits to select output discharge function for Discharge Resistor (LDO\_DIS Register), "1": Enable. "0": Disable.

#### **Input and output Capacitor**

The LDO1/2 are designed to be stable for ceramic output capacitors with Effective capacitance in the range from  $4.7\mu F$  to  $47~\mu F$ . The LDO3~LDO7 are designed to be stable for ceramic output capacitors with Effective capacitance in the range from  $0.68~\mu F$  to  $10~\mu F$ .

The device is also stable with multiple capacitors in parallel, having the total effective capacitance in the specified range. In applications where no low input supplies impedance available, the recommended  $C_{VSYS}$ ,  $C_{VIN34}$ ,  $C_{VIN5}$ ,  $C_{VIN6}$ ,  $C_{VIN7}$ , Capacitance  $\geq 1$ uF and  $C_{VIN12} = \geq 4.7$ uF.

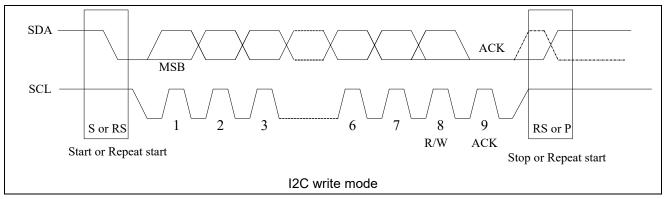

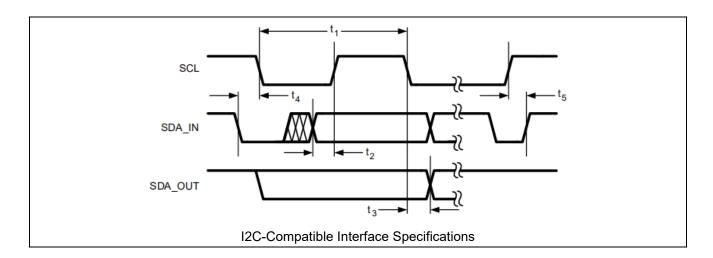

#### Serial Port Interface (I2C)

#### Bus Interface

Baseband Processor can transmit data with ET5907 each other through SDA and SCL port. SDA and SCL composite bus interface, and a pull-up resistor to the power supply should be connected.

#### Data Validity

When the SCL signal is HIGH, the data of SDA port is valid and stable. Only when the SCL signal is low, the level on the SDA port can be changed.

#### • Start (Re-start) and Stop Working Conditions

When the SCL signal is high, SDA signal from high to low represents start or re-start working conditions, while the SCL signal is high, SDA signal from low to high represents stop working conditions.

#### Byte format

Each byte of data line contains 8 bits, which contains an acknowledge bit. The first data is transmitted MSB.

#### Acknowledge

During the writing mode, ET5907 will send a low level response signal with one period width to the SDA port. During the reading mode, ET5907 will not send response signal and the host will send a high response signal one period width to the SDA.

#### Note:

ACK=Acknowledge

MSB=Most Significant Bit

S=Start Conditions RS=Restart Conditions P=Stop Conditions

Fastest Transmission Speed =1000KBITS/S

Restart: SDA-level turnover as expressed by the dashed line waveform

#### • I2C Slave Address

The default 7bit I2C slave address is 0110101b(0x35), and 8bit address for the writing register mode is 01101010b(0x6A), the reading register mode is 01101011b(0x6B). The I2C address can also be changed by setting the 2 bits in register 0x12, i2c\_adr\_sel[1:0] register bits reflects the default options available for request. The Address register will be cleared back to default setting anytime a power-on-reset POR or when a software reset is implemented in the SOFT RESET register.

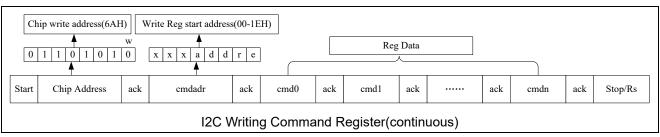

#### • I2C Writing Command Register Interface Protocol (continuous):

Start=Start Conditions

- Chip address=Write register address =0110101+0(w)b

- ack=Acknowledge from ET5907

- Write Reg start address byte = cmdadr(xxx + REG's 5bit addre)

- ack=Acknowledge from ET5907

- Reg data 0 = cmd0(Command data0)

- ack=Acknowledge from ET5907

- ...........

- Reg data n =cmdn(Command datan)

- ack=Acknowledge from ET5907

- Stop/Rs=Stop Condition/Restart Condition

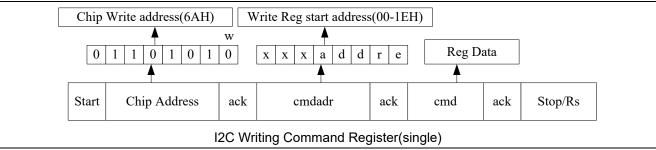

#### • I2C Writing Command Register Interface Protocol (single):

- Start=Start Conditions

- Chip address =Write register address=0110101+0(w)b

- ack=Acknowledge from ET5907

- Write Reg start address byte = cmdadr(xxx + REG's 5bit addre)

- ack=Acknowledge from ET5907

- Reg data= cmd(Command data)

- ack=Acknowledge from ET5907

- Stop/Rs=Stop Condition/Restart Condition

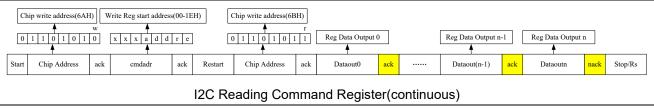

#### • I2C Reading Command Register Interface Protocol(continuous)

Start=Start Conditions

- Chip address =Write register address=0110101+0(w)b

- ack=Acknowledge from ET5907

- Write Reg start address byte = cmdadr(xxx + REG's 5bit addre)

- ack=Acknowledge from ET5907

- Restart=Restart condition

- Chip address Read register address=0110101+1(r)b

- ack=Acknowledge from ET5907

- Dataout0=Register data output 0

- ack=Acknowledge from Host

- ......

- Dataoutn=Register data output n

- nack=No Acknowledge from Host

- Stop/Rs=Stop Condition/Restart Condition

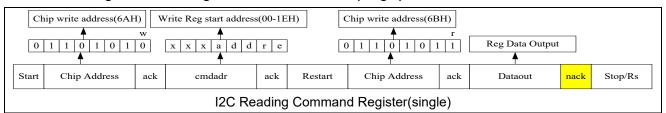

#### • I2C Reading Command Register Interface Protocol(single)

- Start=Start Conditions

- Chip address = Write register address = 0110101+0(w)b

- ack=Acknowledge from ET5907

- Write Reg start address byte = cmdadr(xxx + REG's 5bit addre)

- ack=Acknowledge from ET5907

- Restart=Restart condition

- Chip address Read register address=0110101+1(r)b

- ack=Acknowledge from ET5907

- Dataout=Register data output

- nack=No Acknowledge from Host

- Stop/Rs=Stop Condition/Restart Condition

#### Register Map

| Addr   | Name       | RST   | Bit7      | Bit6                                | Bit5         | Bit4          | Bit3         | Bit2         | Bit1          | Bit0         |

|--------|------------|-------|-----------|-------------------------------------|--------------|---------------|--------------|--------------|---------------|--------------|

| 0X00   | CHIPID     | 0X01  |           | 000000                              |              |               |              |              | chip_         | id[1:0]      |

| 0x01   | VERID      | 0x00  |           | 000000                              |              |               |              |              | ver_i         | d[1:0]       |

| 0x02   | LDO_ILIMIT | 0x7F  | 0         | ldo7_ilimt                          | ldo6_ilimt   | ldo5_ilimt    | ldo4_ilimt   | ldo3_ilimt   | ldo2_ilimt    | ldo1_ilimt   |

| 0x03   | LDO_EN     | 0x00  | 0         | ldo7_en                             | ldo6_en      | ldo5_en       | ldo4_en      | ldo3_en      | ldo2_en       | ldo1_en      |

| 0x04   | LDO1_VSET  | 0x64  |           | •                                   | •            | ldo1_         | vset[7:0]    | •            | 1             | 1            |

| 0x05   | LDO2_VSET  | 0x64  |           |                                     |              | ldo2_         | vset[7:0]    |              |               |              |

| 0x06   | LDO3_VSET  | 0xA0  |           |                                     |              | ldo3_         | vset[7:0]    |              |               |              |

| 0x07   | LDO4_VSET  | 0xA0  |           |                                     |              | ldo4_         | vset[7:0]    |              |               |              |

| 0x08   | LDO5_VSET  | 0xA0  |           |                                     |              | ldo5_         | vset[7:0]    |              |               |              |

| 0x09   | LDO6_VSET  | 0xA0  |           |                                     |              | ldo6_         | vset[7:0]    |              |               |              |

| 0x0A   | LDO7_VSET  | 0xA0  |           |                                     |              | ldo7_         | vset[7:0]    |              |               |              |

| 0x0B   | LDO12_SEQ  | 0x00  |           | 00                                  |              | ldo2_seq[2:0] |              |              | ldo1_seq[2:0] |              |

| 0x0C   | LDO34_SEQ  | 0x00  |           | 00                                  |              | ldo4_seq[2:0] |              |              | ldo3_seq[2:0] |              |

| 0x0D   | LDO56_SEQ  | 0x00  |           | 00                                  |              | ldo6_seq[2:0] |              |              | ldo5_seq[2:0] |              |

| 0x0E   | LDO7_SEQ   | 0x00  |           |                                     | 00000        |               |              |              | ldo7_seq[2:0] |              |

| 0x0F   | SEQ_CTR    | 0x00  | seq_s     | seq_speed[1:0] seq_ctrl[1:0] seq_on |              |               |              |              | seq_cnt[2:0]  |              |

| 0x10   | LDO_DIS    | 0x7F  | 0         | ldo7_dis                            | ldo6_dis     | ldo5_dis      | ldo4_dis     | ldo3_dis     | ldo2_dis      | ldo1_dis     |

| 0x11   | RESET      | 0x07  |           | soft_r                              | eset[3:0]    |               | 0            | ocp_tir      | ne[1:0]       | flt_sd_b     |

| 0x12   | I2C_ADDR   | 0x01  |           |                                     | 00           | 0000          |              |              | I2C_add       | r_sel[1:0]   |

| 0x13   | Reserved   | 0x00  |           |                                     |              |               |              |              |               |              |

| 0x14   | Reserved   | 0x00  |           |                                     |              |               |              |              |               |              |

| 0x15   | UVP_INT    | 0x00  | 0         | ldo6_uvp_int                        | ldo6_uvp_int | ldo5_uvp_int  | ldo4_uvp_int | ldo3_uvp_int | ldo2_uvp_int  | ldo1_uvp_int |

| 0x16   | OCP_INT    | 0x00  | 0         | ldo7_ocp_int                        | Ido6_ocp_int | ldo5_ocp_int  | ldo4_ocp_int | Ido3_ocp_int | ldo2_ocp_int  | ldo1_ocp_int |

| 0x17   | TSD_UVLO   | 0x00  | tod int   | tod wrn int                         | vsys_uvlo    | ldo7_uvlo     | ldo6_uvlo    | ldo5_uvlo    | ldo34_uvlo    | ldo12_uvlo   |

| UX 17  | _INT       | 0000  | tsd_int   | tsd_wrn_int                         | _int         | _int          | _int         | _int         | _int          | _int         |

| 0x18   | UVP_STAU   | 0x00  | 0         | ldo7_uvp                            | ldo6_uvp     | ldo5_uvp      | ldo4_uvp     | ldo3_uvp     | ldo2_uvp      | ldo1_uvp     |

| 0.00   | 0VI _01A0  | 0,000 | · ·       | _stau                               | _stau        | _stau         | _stau        | _stau        | _stau         | _stau        |

| 0x19   | OCP_STAU   | 0x00  | 0         | ldo7_ocp                            | ldo6_ocp     | ldo5_ocp      | ldo4_ocp     | ldo3_ocp     | ldo2_ocp      | ldo1_ocp     |

| 0.713  | 001_01740  | 0,000 | Ů         | _stau                               | _stau        | _stau         | _stau        | _stau        | _stau         | _stau        |

| 0x1A   | TSD_UVLO   | 0x00  | tsd_ stau | tsd_wrn                             | vsys_uvlo    | ldo7_uvlo     | ldo6_uvlo    | ldo5_uvlo    | ldo34_uvlo    | ldo12_uvlo   |

| 0,11,1 | _STAU      | 0,00  | 154_5144  | _stau                               | _stau        | _stau         | _stau        | _stau        | _stau         | _stau        |

| 0x1B   | SUSD_STA   | 0x00  | chip_susd | ldo7_susd                           | ldo6_susd    | ldo5_susd     | ldo4_susd    | ldo3_susd    | ldo2_susd     | ldo1_susd    |

| OXID   | U          | 0,00  | _stau     | _stau                               | _stau        | _stau         | _stau        | _stau        | _stau         | _stau        |

| 0x1C   | UVP_INTMA  | 0x00  | 0         | ldo7_uvp                            | ldo6_uvp     | ldo5_uvp      | ldo4_uvp     | ldo3_uvp     | ldo2_uvp      | ldo1_uvp     |

|        |            | 0,100 |           | _mask                               | _mask        | _mask         | _mask        | _mask        | _mask         | _mask        |

| 0x1D   | OCP_INTMA  | 0x00  | 0         | ldo7_ocp                            | ldo6_ocp     | ldo5_ocp      | ldo4_ocp     | ldo3_ocp     | ldo2_ocp      | ldo1_ocp     |

|        |            |       |           | _mask                               | _mask        | _ mask        | _mask        | _mask        | _mask         | _mask        |

| 0x1E   | TSD_UVLO   | 0x00  | tsd_mask  | tsd_wrn                             | vsys_uvlo    | ldo7_uvlo     | ldo6_uvlo    | ldo5_uvlo    | ldo34_uvlo    | ldo12_uvlo   |

|        | _INTMA     |       | _         | _mask                               | _mask        | _mask         | _mask        | _mask        | _mask         | _mask        |

- 0x00 CHIPID Register---- Indicates the product ID with revision. Default=0x01 type: Read only chip\_id[1:0] Indicates the product ID with revision. Read only.

- 0x01 VERID Register---- Indicates the device ID with revision. Default = 0x00 type: Read only ver\_id[1:0] Indicates the device ID with revision. Read only.

- 0x02 LDO\_ILIMIT Register ----LDO Current Limit Selection. Default = 0x7F

The detail current limit threshold value is shown in the table as below:

| Bit | Name       | Default | Туре | Description                                         |  |  |  |

|-----|------------|---------|------|-----------------------------------------------------|--|--|--|

| 7   | Rev.       | 0       | R    | Reserved                                            |  |  |  |

|     |            |         |      | LDO7 current limit threshold value:                 |  |  |  |

| 6   | ldo7_ilimt | 1       | R/W  | 0b: current limit~420mA short current limit~ 35mA   |  |  |  |

|     |            |         |      | 1b: current limit~550mA short current limit~ 45mA   |  |  |  |

|     |            |         |      | LDO6 current limit threshold value:                 |  |  |  |

| 5   | ldo6_ilimt | 1       | R/W  | 0b: current limit~420mA short current limit~ 35mA   |  |  |  |

|     |            |         |      | 1b: current limit~550mA short current limit~ 45mA   |  |  |  |

|     |            |         |      | LDO5 current limit threshold value:                 |  |  |  |

| 4   | ldo5_ilimt | 1       | R/W  | 0b: current limit~420mA short current limit~ 35mA   |  |  |  |

|     |            |         |      | 1b: current limit~550mA short current limit~ 45mA   |  |  |  |

|     |            |         |      | LDO4 current limit threshold value:                 |  |  |  |

| 3   | ldo4_ilimt | 1       | R/W  | 0b: current limit~420mA short current limit~ 35mA   |  |  |  |

|     |            |         |      | 1b: current limit~550mA short current limit~ 45mA   |  |  |  |

|     |            |         |      | LDO3 current limit threshold value:                 |  |  |  |

| 2   | ldo3_ilimt | 1       | R/W  | 0b: current limit~420mA short current limit~ 35mA   |  |  |  |

|     |            |         |      | 1b: current limit~550mA short current limit~ 45mA   |  |  |  |

|     |            |         |      | LDO2 current limit threshold value:                 |  |  |  |

| 1   | ldo2_ilimt | 1       | R/W  | 0b: current limit~1200mA short current limit~ 300mA |  |  |  |

|     |            |         |      | 1b: current limit~1400mA short current limit~ 350mA |  |  |  |

|     |            |         |      | LDO1 current limit threshold value:                 |  |  |  |

| 0   | ldo1_ilimt | 1       | R/W  | 0b: current limit~1200mA short current limit~ 300mA |  |  |  |

|     |            |         |      | 1b: current limit~1400mA short current limit~ 350mA |  |  |  |

• 0x03 LDO\_EN Register ----LDOs Chip enable control register. Default = 0x00

LDO enable control register by I2C while the register value of Idox\_seq[2:0] are set to be default "000". This register can be written to enable or disable the corresponding LDO regulator.

| Bit | Name    | Default | Туре  | Description            |  |  |

|-----|---------|---------|-------|------------------------|--|--|

| 7   | Rev.    | 0       | R     | Reserved               |  |  |

| 6   | ldo7 on | 0       | R/W   | LDO7 enable control:   |  |  |

| 0   | ldo7_en | U       | IT/VV | 0b: Disable 1b: Enable |  |  |

| 5 | Ido6 on         | 0     | R/W                    | LDO6 enable control:   |  |

|---|-----------------|-------|------------------------|------------------------|--|

| 5 | ldo6_en         | 0     | FK/VV                  | 0b: Disable 1b: Enable |  |

| 4 | ldo5 en         | 0     | R/W                    | LDO5 enable control:   |  |

| 4 | 1005_611        | O     | IX/VV                  | 0b: Disable 1b: Enable |  |

| 3 | ldo4 on         | 0     | R/W                    | LDO4 enable control:   |  |

| 3 | 3   Ido4_en   0 | FK/VV | 0b: Disable 1b: Enable |                        |  |

| 2 | ldo3 en         | 0     | R/W                    | LDO3 enable control:   |  |

|   | 1003_611        | O     | FX/ V V                | 0b: Disable 1b: Enable |  |

| 1 | ldo2 en         | 0     | R/W                    | LDO2 enable control:   |  |

| ' | ldoz_en         | O     | FX/VV                  | 0b: Disable 1b: Enable |  |

| 0 | ldo1 on         | 0     | R/W                    | LDO1 enable control:   |  |

|   | ldo1_en         | 0     | FX/VV                  | 0b: Disable 1b: Enable |  |

- 0x04 LDO1 Register ---- LDO1 output voltage setting register. Default = 0x64 Type: R/W

- 0x05 LDO2 Register ---- LDO2 output voltage setting register. Default = 0x64 Type: R/W

The register LDO1/2\_VSET[7:0] set the voltage of LDO1/ LDO2, it have 200 steps, shown as below table, the formula is VOUT =0.600V + [d\*6mV];

|         | LDO1/LDO2 Output Voltage set by LDO1/2_VSET[7:0] |                   |  |  |  |  |  |  |  |

|---------|--------------------------------------------------|-------------------|--|--|--|--|--|--|--|

| Dec     | Binary                                           | Output Voltage(V) |  |  |  |  |  |  |  |

| 0       | 0000000                                          | 0.600             |  |  |  |  |  |  |  |

| 1       | 0000001                                          | 0.606             |  |  |  |  |  |  |  |

| 2       | 0000010                                          | 0.612             |  |  |  |  |  |  |  |

| 3       | 0000011                                          | 0.618             |  |  |  |  |  |  |  |

|         |                                                  |                   |  |  |  |  |  |  |  |

| 33      | 00100001                                         | 0.798             |  |  |  |  |  |  |  |

| 34      | 00100011                                         | 0.804             |  |  |  |  |  |  |  |

| 35      | 00100100                                         | 0.810             |  |  |  |  |  |  |  |

|         |                                                  |                   |  |  |  |  |  |  |  |

| 100     | 01100100(default)                                | 1.200             |  |  |  |  |  |  |  |

| 101     | 01100101                                         | 1.206             |  |  |  |  |  |  |  |

| 102     | 01100110                                         | 1.212             |  |  |  |  |  |  |  |

|         |                                                  |                   |  |  |  |  |  |  |  |

| 200     | 11001000                                         | 1.8               |  |  |  |  |  |  |  |

| 201~255 |                                                  |                   |  |  |  |  |  |  |  |

VOUT is less than 0.8V, which is not recommended. If you need to use it, please contact us.

# 0x06~0x0A LDO3~7 Register ---- LDO3~7 output voltage setting register. Default = 0xA0 Type: R/W

The registers LDO3~7\_VSET[7:0] set the voltage of LDO3~LDO7, each voltage have 226 steps, shown as below table, the formula is VOUT=1.200V + [d\*10mV].

| LDO1/LDO2 Output Voltage set by LDO1/2_VSET[7:0] |                   |                   |  |  |  |  |  |

|--------------------------------------------------|-------------------|-------------------|--|--|--|--|--|

| Dec                                              | Binary            | Output Voltage(V) |  |  |  |  |  |

| 0~29                                             | 00000000~00011101 | Reservedd         |  |  |  |  |  |

| 30                                               | 00011110          | 1.500             |  |  |  |  |  |

| 31                                               | 00011111          | 1.510             |  |  |  |  |  |

| 32                                               | 00100000          | 1.520             |  |  |  |  |  |

| 33                                               | 00100001          | 1.530             |  |  |  |  |  |

| 34                                               | 00100010          | 1.540             |  |  |  |  |  |

|                                                  |                   |                   |  |  |  |  |  |

| 160                                              | 10100000(default) | 2.8V              |  |  |  |  |  |

| 161                                              | 10100001          | 2.810             |  |  |  |  |  |

| 162                                              | 10100010          | 2.820             |  |  |  |  |  |

|                                                  |                   |                   |  |  |  |  |  |

| 255                                              | 1111111           | 3.750             |  |  |  |  |  |

#### ■ 0x0B~0x0E LDO12/34/56/7\_SEQ Register ---- Power sequence setting register. Default = 0x00

Power sequence setting register. there are 7 time slots defined as following table. The power-up sequence is start from slot1 to slot7, and shut down start from slot7 to slot1. Power-up and shut down of each LDO regulator can be set at any one of the slots.

| ldox_seq[2:0] | VOUTX                              |

|---------------|------------------------------------|

| 000           | Controlled by I2C register Idox_en |

| 001           | Slot1                              |

| 010           | Slot2                              |

| 011           | Slot3                              |

| 100           | Slot4                              |

| 101           | Slot5                              |

| 110           | Slot6                              |

| 111           | Slot7                              |

## • 0x0F SEQ\_CTR Register ---- Power sequence setting and status register. Default = 0x00

| Bit | Name                 | Default | Туре | Description                                                      |                                      |                                    |  |  |

|-----|----------------------|---------|------|------------------------------------------------------------------|--------------------------------------|------------------------------------|--|--|

|     |                      |         |      | Define the slot period                                           | Define the slot period as following: |                                    |  |  |

|     |                      |         |      | Register V                                                       | alue                                 | Slot period(ms)                    |  |  |

| 7:6 | 7:6   seq_speed[1:0] | 00      | R/W  | 00                                                               |                                      | 0.5                                |  |  |

| '   |                      |         |      | 01                                                               |                                      | 1.0                                |  |  |

|     |                      |         |      | 10                                                               |                                      | 1.5                                |  |  |

|     |                      |         |      | 11                                                               |                                      | 2.0                                |  |  |

|     |                      |         |      | Enables power-up                                                 | or shut down                         | of SEQ:                            |  |  |

|     |                      |         |      | Register Value                                                   |                                      | Description                        |  |  |

|     |                      |         |      | 00                                                               | Default                              |                                    |  |  |

| 5:4 | 000 otrl[1:0]        | 00      | W/C  | 01                                                               | Starts an L                          | DO power up sequence               |  |  |

| 5.4 | seq_ctrl[1:0]        | 00      | VV/C | 10                                                               | Starts an L                          | DO shutdown sequence               |  |  |

|     |                      |         |      | 11                                                               | Bit configur                         | ration is ignored                  |  |  |

|     |                      |         |      | Note: The bits will always clear immediately when written to and |                                      |                                    |  |  |

|     |                      |         |      | always read back 0                                               | 0.                                   | •                                  |  |  |

|     |                      |         |      | Indicates the activation signal of SEQ.                          |                                      |                                    |  |  |

|     |                      |         |      | 0b: Indicates that the sequencing is not in process              |                                      |                                    |  |  |

| 3   | 200 00               |         | В    | 1b: Indicates that the sequencing is executing and somewhere     |                                      |                                    |  |  |

| 3   | seq_on               | 0       | R    | between the start of                                             | f slot 1 and tl                      | ne end of slot 7. The bit remains  |  |  |

|     |                      |         |      | a 1 until slot 7 has o                                           | completed at                         | start-up or slot 1 has finished at |  |  |

|     |                      |         |      | shutdown, regardle                                               | ss of what sl                        | ots are used.                      |  |  |

|     |                      |         |      | Indicates the slot nu                                            | umber of SE                          | Q at the moment:                   |  |  |

|     |                      |         |      | Register Value                                                   |                                      | SEQ Counter                        |  |  |

|     |                      |         |      | 000                                                              | Sequencing                           | g has completed or not started     |  |  |

|     |                      |         |      | 001                                                              | Indicates w                          | as in slot 1 during register read  |  |  |

| 2:0 | seq_cnt[2:0]         | 0       | R    | 010                                                              | Indicates w                          | as in slot 2 during register read  |  |  |

| 0   | 554_5/142.0]         |         | '`   | 011                                                              | Indicates w                          | as in slot 3 during register read  |  |  |

|     |                      |         |      | 100                                                              | Indicates w                          | as in slot 4 during register read  |  |  |

|     |                      |         |      | 101                                                              | Indicates w                          | as in slot 5 during register read  |  |  |

|     |                      |         |      | 110                                                              | Indicates w                          | as in slot 6 during register read  |  |  |

|     |                      |         |      | 111                                                              | Indicates w                          | as in slot 7 during register read  |  |  |

## 0x10 LDO\_DIS Register ----Discharge Resistor Selection. Default = 0x7F

Each LDO regulators output discharge resistor enable control.

| Bit | Name     | Default | Туре | Description                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Rev.     | 0       | R    | Reserved                                                                                                                                                                                                                                                                                                                                           |

| 6   | ldo7_dis | 1       | R/W  | LDO7 Discharge Enabled/Disabled control:  0b: Disable Pull down will not be activated when LDO7 is disabled by any event 1b: Enable Pull down will be activated when LDO7 is disabled by RESET_N going low or Ido7_en=0 or a Sequenced shutdown or Ido7_susd_stau=1(VIN7_UVLO/LDO7_OCP/LDO7_UVP event) or chip_susd_stau=1(TSD or VSYS_UVLO event) |

| 5   | ldo6_dis | 1       | R/W  | LDO6 Discharge Enabled/Disabled control:  0b: Disable Pull down will not be activated when LDO6 is disabled by any event 1b: Enable Pull down will be activated when LDO6 is disabled by RESET_N going low or Ido6_en=0 or a Sequenced shutdown or Ido6_susd_stau=1(VIN6_UVLO/LDO6_OCP/LDO6_UVP event) or chip_susd_stau=1(TSD or VSYS_UVLO event) |

| 4   | ldo5_dis | 1       | R/W  | LDO5 Discharge Enabled/Disabled control:  0b: Disable Pull down will not be activated when LDO5 is disabled by any event 1b: Enable Pull down will be activated when LDO5 is disabled by RESET_N going low or Ido5_en=0 or a Sequenced shutdown or Ido5_susd_stau=1(VIN5_UVLO/LDO5_OCP/LDO5_UVP event) or chip_susd_stau=1(TSD or VSYS_UVLO event) |

| 3   | ldo4_dis | 1       | R/W  | LDO4 Discharge Enabled/Disabled control:  0b: Disable Pull down will not be activated when LDO4 is disabled by any event 1b: Enable Pull down will be activated when LDO4 is disabled by RESET_N going low or Ido4_en=0 or a Sequenced shutdown or Ido4_susd_stau=1(VIN4_UVLO/LDO4_OCP/LDO4_UVP event) or chip_susd_stau=1(TSD or VSYS_UVLO event) |

|   |            |   |       | T                                                                  |

|---|------------|---|-------|--------------------------------------------------------------------|

|   |            |   |       | LDO3 Discharge Enabled/Disabled control:                           |

|   |            |   |       | 0b: Disable                                                        |

|   |            |   |       | Pull down will not be activated when LDO3 is disabled by any event |

| 2 | ldo3 dis   | 1 | R/W   | 1b: Enable                                                         |

|   | iuos_uis   | 1 | FX/VV | Pull down will be activated when LDO3 is disabled by RESET_N going |

|   |            |   |       | low or Ido3_en=0 or a Sequenced shutdown or                        |

|   |            |   |       | ldo3_susd_stau=1(VIN3_UVLO/LDO3_OCP/LDO3_UVP event) or             |

|   |            |   |       | chip_susd_stau=1(TSD or VSYS_UVLO event)                           |

|   |            |   |       | LDO2 Discharge Enabled/Disabled control:                           |

|   |            |   | R/W   | 0b: Disable                                                        |

|   |            | 1 |       | Pull down will not be activated when LDO2 is disabled by any event |

|   |            |   |       | 1b: Enable                                                         |

| 1 | ldo2_dis   |   |       | Pull down will be activated when LDO2 is disabled by RESET_N going |

|   |            |   |       | low or Ido2_en=0 or a Sequenced shutdown or                        |

|   |            |   |       | ldo2_susd_stau=1(VIN12_UVLO/LDO2_OCP/LDO2_UVP event) or            |

|   |            |   |       | chip_susd_stau=1(TSD or VSYS_UVLO event)                           |

|   |            |   |       | LDO1 Discharge Enabled/Disabled control:                           |

|   |            |   |       | 0b: Disable                                                        |

|   |            |   |       | Pull down will not be activated when LDO1 is disabled by any event |

|   | 1.1.4 .15. | 4 | D/M   | 1b: Enable                                                         |

| 0 | ldo1_dis   | 1 | R/W   | Pull down will be activated when LDO1 is disabled by RESET_N going |

|   |            |   |       | low or Ido1_en=0 or a Sequenced shutdown or                        |

|   |            |   |       | ldo1_susd_stau=1(VIN12_UVLO/LDO1_OCP/LDO1_UVP event) or            |

|   |            |   |       | chip_susd_stau=1(TSD or VSYS_UVLO event)                           |

## ■ 0x11 RESET Register ----LDOs reset control register. Default = 0x07

| Bit | Name            | Default | Туре |                       | Description                                                                                                                         |

|-----|-----------------|---------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | soft_reset[3:0] | 0000    | W/C  | their default values. | gins a soft reset of the device I2C registers to This bit is cleared upon execution of the other value than "1011" will be ignored. |

| 3   | Rev.            | 0       | R    | Reserved.             |                                                                                                                                     |

|     | ocp_time[1:0]   | 11      | R/W  | •                     | of the length of the deglitch timer for current fore a fault is triggered:  Slot period(us)                                         |

| 2:1 |                 |         |      | 00                    | 125                                                                                                                                 |

|     |                 |         |      | 01                    | 250                                                                                                                                 |

|     |                 |         |      | 10                    | 500                                                                                                                                 |

|     |                 |         |      | 11                    | 1000                                                                                                                                |

|   | I        | 1 | 1   | T                                                                       |

|---|----------|---|-----|-------------------------------------------------------------------------|

|   |          |   |     | Prevents Shutdown When a Fault Occurs:                                  |

|   |          |   |     | 0b: LDO is shutdown if a UVP or OCP event occurs or if the              |

|   |          |   |     | LDO's input VIN12, VIN34, VIN5, VIN6 or VIN7 have a                     |

|   |          |   |     | UVLO event. Each shutdown time is about 20ms, then                      |

|   |          |   |     | restart again, when the times of shutdown are arrived to                |

|   |          |   |     | three, the according register bit ldox_en will be cleared.              |

|   |          |   |     | All LDO(s) are shutdown if a VSYS UVLO or TSD event                     |

|   |          |   |     | occurs. Each shutdown time is about 20ms, then restart                  |

|   |          |   |     | again, when the times of shutdown are arrived to four, the              |

|   |          |   |     | according register bit ldox_en will be cleared.                         |

| 0 | flt_sd_b | 1 | R/W | Notes:                                                                  |

|   |          |   |     | If this bit function is desired, flt_sd_b should be set to "0" prior to |

|   |          |   |     | enabling any LDOs after a Power-On-Reset.                               |

|   |          |   |     | 1b: LDO is not shutdown if a UVP or OCP event occurs. If the            |

|   |          |   |     | LDO's input VIN12, VIN34, VIN5, VIN6 or VIN7 have a                     |

|   |          |   |     | UVLO event, the associated LDO will be shutdown until the               |

|   |          |   |     | supply returns, but the fault will not be counted.                      |

|   |          |   |     | If a VSYS UVLO or TSD event occurs, All LDO(s) will be                  |

|   |          |   |     | shutdown until the VSYS supply returns and TSD is                       |

|   |          |   |     | released, but the fault will not be counted.                            |

## ■ 0x12 ADDR Register ---- I2C address select register. Default = 0x01

| Bit | Name              | Default | Туре |                               | Description                                    |

|-----|-------------------|---------|------|-------------------------------|------------------------------------------------|

| 7:2 | Rev.              | 000000  | R    | Reserved.                     |                                                |

|     |                   | 01      | R/W  | Tunnel bits to chang address: | e value for customer to select a different I2C |

|     |                   |         |      | Register Value                | I2C Address Settings                           |

| 1:0 | i2c_addr_sel[1:0] |         |      | 00                            | 0x20                                           |

|     |                   |         |      | 01                            | 0x35                                           |

|     |                   |         |      | 10                            | 0x61                                           |

|     |                   |         |      | 11                            | 0x72                                           |

## ■ 0x15 UVP\_INT Register ---- LDO UVP Interrupt register. Default = 0x00

| Bit | Name          | Default | Туре  | Description                                                            |

|-----|---------------|---------|-------|------------------------------------------------------------------------|

| 7   | Rev.          | 0       | R     | Reserved                                                               |

|     |               |         |       | LDO7 UVP Interrupt:                                                    |

| 6   | ldo7_uvp_int  | 0       | R/C   | 0b: Clear                                                              |

| 0   | ido7_uvp_iiit | U       | K/C   | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |               |         |       | 1b: Under-Voltage event detected on the LDO7 output.                   |

|     |               |         |       | LDO6 UVP Interrupt:                                                    |

| 5   | Ido6 uum int  | 0       | R/C   | 0b: Clear                                                              |

| 5   | ldo6_uvp_int  | U       | R/C   | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |               |         |       | 1b: Under-Voltage event detected on the LDO6 output.                   |

|     |               |         |       | LDO5 UVP Interrupt:                                                    |

| 1   | lala E int    | 0       | R/C   | 0b: Clear                                                              |

| 4   | ldo5_uvp_int  | 0       | R/C   | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |               |         |       | 1b: Under-Voltage event detected on the LDO5 output.                   |

|     |               | 0       | D. (0 | LDO4 UVP Interrupt:                                                    |

|     | lala 4 int    |         |       | 0b: Clear                                                              |

| 3   | ldo4_uvp_int  |         | R/C   | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |               |         |       | 1b: Under-Voltage event detected on the LDO4 output.                   |

|     |               |         |       | LDO3 UVP Interrupt:                                                    |

| 2   | lala O int    |         | R/C   | 0b: Clear                                                              |

| 2   | ldo3_uvp_int  | 0       | R/C   | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |               |         |       | 1b: Under-Voltage event detected on the LDO3 output.                   |

|     |               |         |       | LDO2 UVP Interrupt:                                                    |

|     | IdaOm int     | 0       | R/C   | 0b: Clear                                                              |

| 1   | ldo2_uvp_int  | 0       | R/C   | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |               |         |       | 1b: Under-Voltage event detected on the LDO2 output.                   |

|     |               |         |       | LDO1 UVP Interrupt:                                                    |

|     | ldo1 :=t      | 0       | R/C   | 0b: Clear                                                              |

| 0   | ldo1_uvp_int  | 0       | K/C   | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |               |         |       | 1b: Under-Voltage event detected on the LDO1 output.                   |

### • 0x16 OCP\_INT Register ---- LDO OCP Interrupt Register. Default = 0x00

| Bit | Name         | Default | Туре | Description                                                                                                                                              |

|-----|--------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Rev.         | 0       | R    | Reserved                                                                                                                                                 |

| 6   | ldo7_ocp_int | 0       | R/C  | LDO7 OCP Interrupt : 0b:Clear It can be cleared by reading this register or setting RESET_N pin to 0 1b: Over current event detected on the LDO7 output. |

|   | 1              |   |     | · · · · · · · · · · · · · · · · · · ·                                  |

|---|----------------|---|-----|------------------------------------------------------------------------|

|   |                | 0 | R/C | LDO6 OCP Interrupt :                                                   |

| 5 | Ido6 oon int   |   |     | 0b:Clear                                                               |

| 3 | ldo6_ocp_int   | U | R/C | It can be cleared by reading this register or setting RESET_N pin to 0 |

|   |                |   |     | 1b: Over current event detected on the LDO6 output.                    |

|   |                |   |     | LDO5 OCP Interrupt :                                                   |

|   | Ido Coon int   | 0 | R/C | 0b:Clear                                                               |

| 4 | ldo5_ocp_int   | 0 | R/C | It can be cleared by reading this register or setting RESET_N pin to 0 |

|   |                |   |     | 1b: Over current event detected on the LDO5 output.                    |

|   |                |   |     | LDO4 OCP Interrupt :                                                   |

|   | 14-4 :         | 0 | D/O | 0b:Clear                                                               |

| 3 | Ido4_ocp_int   | 0 | R/C | It can be cleared by reading this register or setting RESET_N pin to 0 |

|   |                |   |     | 1b: Over current event detected on the LDO4 output.                    |

|   |                | 0 |     | LDO3 OCP Interrupt :                                                   |

|   | Ida O a an int |   | D/C | 0b:Clear                                                               |

| 2 | ldo3_ocp_int   |   | R/C | It can be cleared by reading this register or setting RESET_N pin to 0 |

|   |                |   |     | 1b: Over current event detected on the LDO3 output.                    |

|   |                |   |     | LDO2 OCP Interrupt :                                                   |

|   | 14-0 :         | 0 | D/O | 0b:Clear                                                               |

| 1 | ldo2_ocp_int   | 0 | R/C | It can be cleared by reading this register or setting RESET_N pin to 0 |

|   |                |   |     | 1b: Over current event detected on the LDO2 output.                    |

|   |                |   |     | LDO1 OCP Interrupt :                                                   |

|   | 11.4           | _ |     | 0b:Clear                                                               |

| 0 | ldo1_ocp_int   | 0 | R/C | It can be cleared by reading this register or setting RESET_N pin to 0 |

|   |                |   |     | 1b: Over current event detected on the LDO1 output.                    |

## • 0x17 TSD\_UVLO\_INT Register ---- TSD and UVLO Interrupt Register. Default = 0x00

| Bit | Name           | Default | Туре | Description                                                            |

|-----|----------------|---------|------|------------------------------------------------------------------------|

|     |                |         |      | Thermal Shutdown Interrupt:                                            |

|     |                |         |      | 0b: Clear                                                              |

| 7   | tsd_int        | 0       | R/C  | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |                |         |      | 1b: A Thermal Shutdown event detected or that the temperature has      |

|     |                |         |      | fallen below the hysteresis level.                                     |

|     |                | 0       | R/C  | Thermal Warning Interrupt:                                             |

|     |                |         |      | 0b: Clear                                                              |

| 6   | tsd_wrn_int    |         |      | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |                |         |      | 1b: Thermal Shutdown Warning threshold was surpassed or that the       |

|     |                |         |      | temperature has fallen below the hysteresis level.                     |

|     |                |         |      | VSYS Under-Voltage-Lock-Out Interrupt:                                 |

| 5   | vsys_uvlo_int  | 0       | R/C  | 0b: Normal operation                                                   |

| 3   | vsys_uvio_iiit |         |      | It can be cleared by reading this register or setting RESET_N pin to 0 |

|     |                |         |      | 1b: Indicates that the VSYS power fell below the UVLO input            |

|   |                   |   |      | threshold or that the supplies have risen above the rising thresholds  |

|---|-------------------|---|------|------------------------------------------------------------------------|

|   |                   |   |      | after a UVLO fault                                                     |

|   |                   |   |      | VIN7 Under-Voltage-Lock-Out Interrupt:                                 |