# ET4557 - SIM Card Interface Level Translator With EMI Filter and ESD Protection

# **General Description**

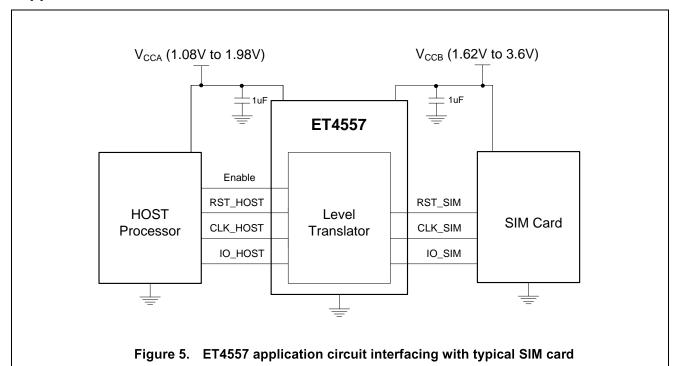

The ET4557 device is built for interfacing a SIM card with a single low-voltage 1.08V to 1.98V host side interface. The ET4557 contains three 1.62V to 3.6V level translators to convert the data, RST and CLK signals between a SIM card and a host micro controller.

The ET4557 is compliant with all ETSI, IMT-2000 and ISO-7816 SIM/Smart card interface requirements.

#### **Features**

- Supports clock speed up to 10MHz clock

- Compliant with all ETSI, IMT-2000 and ISO-7816 SIM/Smart card interface requirements

- Support SIM card supply voltages with range of 1.62V to 3.6V

- Host micro controller operating voltage range: 1.08V to 1.98V

- Automatic level translation of I/O, RST and CLK between SIM card and host side interface with capacitance isolation

- Incorporates shutdown feature for the SIM card signals according to ISO-7816-3

- Automatic enable and disable through VCCB

- Integrated pull-up and pull-down resistors: no external resistors required

- Integrated EMI filters suppress higher harmonics of digital I/Os

- Integrated 8kV ESD protection according to IEC 61000-4-2, level 4 on all SIM card contact pins

- Level shifting buffers keep ESD stress away from the host (zero-clamping concept)

- Pb-free, Restriction of Hazardous Substances (RoHS) compliant and free of halogen and antimony (Dark Green compliant)

- Part No. and Package

| Part No. | Package                         | MSL     |

|----------|---------------------------------|---------|

| ET4557   | QFN10 (1.4mm×1.8mm,0.4mm pitch) | Level 1 |

#### **Applications**

- Mobile and personal phones

- Wireless modems

- SIM card terminals

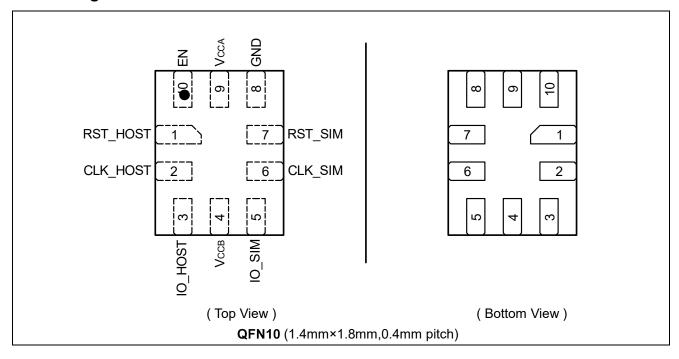

# **Pin Configuration**

# **Pin Function**

| Pin      | Pin No. | Туре   | Description                                                                                                                                                                                    |  |

|----------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RST_HOST | 1       | I      | Reset input from host controller.                                                                                                                                                              |  |

| CLK_HOST | 2       | I      | Clock input from host controller.                                                                                                                                                              |  |

| ю_ноѕт   | 3       | I/O    | Host controller bidirectional data input/output. The host output must be on an open-drain driver.                                                                                              |  |

| Vccb     | 4       | Supply | SIM card supply voltage. When $V_{\text{CCB}}$ is below the $V_{\text{CCB}}$ disable, the device is disabled. This pin should be bypassed with a 1 $\mu F$ ceramic capacitor close to the pin. |  |

| IO_SIM   | 5       | I/O    | SIM card bidirectional data input/output. The SIM card output must be on an open-drain driver.                                                                                                 |  |

| CLK_SIM  | 6       | 0      | Clock output pin for the SIM card.                                                                                                                                                             |  |

| RST_SIM  | 7       | 0      | Reset output pin for the SIM card.                                                                                                                                                             |  |

| GND      | 8       | Ground | Ground for the SIM card and host controller. Proper grounding and bypassing are required to meet ESD specifications.                                                                           |  |

| Vcca     | 9       | Supply | Supply voltage for the host controller side input/output pins (CLK_HOST, RST_HOST, IO_HOST). This pin should be bypassed with a 1 µF ceramic capacitor close to the pin.                       |  |

| EN       | 10      | I      | Host controller driven enable pin. This pin should be HIGH (V <sub>CC</sub> for normal operation, and LOW to help avoid race conditions specifically during the shutdown sequence.             |  |

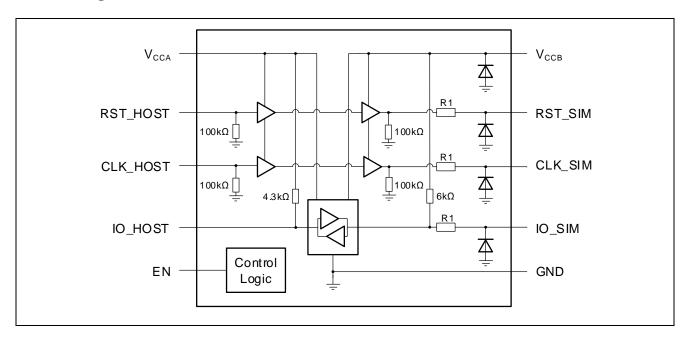

# **Block Diagram**

### **Functional Description**

The ET4557 device is built for interfacing a SIM card with a single low-voltage 1.08V to 1.98V host side interface. The ET4557 contains three 1.62V to 3.6V level translators to convert the data, RST and CLK signals between a SIM card and a host micro controller.

**Supply Voltage** Input/Out Input Operational EN (1)(2) Mode Host SIM Card  $V_{CCA}$ **V**<sub>CCB</sub> 1.08 V to 1.98 V 1.62 V to 3.6 V HOST=SIM Card SIM Card=HOST Active Η 1.08 V to 1.98 V 1.62 V to 3.6 V L See Table 2, Condition B Shutdown Mode 1.62 V to 3.6 V **GND** Χ See Table 2, Condition B Shutdown Mode Χ 1.08 V to 1.98 V **GND** See Table 2, Condition A Shutdown Mode **GND** Χ **GND** See Table 2, Condition A Shutdown Mode

**Table 1. Function Table**

#### Notes:

1) H = HIGH voltage level; L = LOW voltage level; X = don't care.

2)  $V_{IL}$  and  $V_{IH}$  are referenced to  $V_{CCA}$ . The EN can be controlled by an external device limit of  $V_{CCA}$  + 0.3 V.

**Table 2. Pin Condition**

| Pin condition | Condition A                     | Condition B                     |  |

|---------------|---------------------------------|---------------------------------|--|

| RST_HOST      | 100 kΩ pull low                 | 100 kΩ pull low                 |  |

| CLK_HOST      | 100 kΩ pull low                 | 100 kΩ pull low                 |  |

| IO_HOST       | 4.3 kΩ pull to V <sub>CCA</sub> | 4.3 kΩ pull to V <sub>CCA</sub> |  |

| RST_SIM       | 100 kΩ pull low                 | 400 Ω pull low                  |  |

| CLK_SIM       | 100 kΩ pull low                 | 400 Ω pull low                  |  |

| IO_SIM        | High Z                          | 400 Ω pull low                  |  |

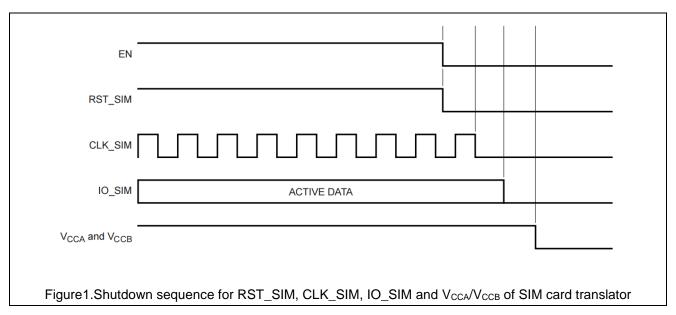

#### **Shutdown Sequence of ET4557**

The ISO 7816-3 specification specifies the shutdown sequence for the SIM card signals to ensure that the card is properly disabled for power savings. Also during hot swap, the orderly shutdown of these signals helps to avoid any improper write and corruption of data.

When the enable, EN, is asserted LOW, the shutdown sequence is initiated by powering down the RST\_SIM channel. Once the RST\_SIM channel is powered down, CLK\_SIM and IO\_SIM are powered down sequentially one-by-one. An internal pull-down resistor on the SIM pins is used to pull these channels LOW. The shutdown sequence is completed in a few microseconds. It is important that EN is pulled LOW before V<sub>CCA</sub> and V<sub>CCB</sub> supplies go LOW to ensure that the shutdown sequence is properly initiated.

#### **Embedded Enable if Enable is tied to VCCA**

The device contains an auto-enable feature. If  $V_{CCB}$  rises above  $V_{CCB\_EN}$ , the level translator logic is enabled automatically. As soon as  $V_{CCB}$  drops below the  $V_{CCB\_DIS}$ , the SIM card side drivers and the level translator logic is disabled. Host side IO pin is configured as input with a 4.3 k $\Omega$  resistor pulled up to  $V_{CCA}$ .

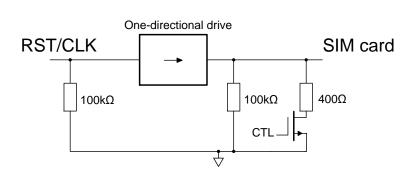

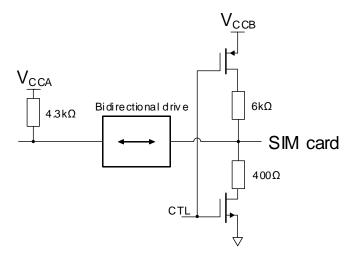

When the  $V_{CCB}$  drops below  $V_{CCB}$  disable voltage but is still higher than a MOS threshold (e.g. 0.8 V) the pull-down NMOS in the one-directional drive will be off and NMOS controlled by CTL will be on, and the 400  $\Omega$  resistor will keep the card side CLK/RST/IO low. Additionally the CLK/RST pins on both the Host and Card side have a 100 k $\Omega$  pull down resistor. The 400  $\Omega$  resistor is used for discharge at power off and the 100 k $\Omega$  resister is used for keep RST\_SIM/CLK\_SIM low when  $V_{CCB}$  below  $V_{TH}$ .

Figure 2. RST/CLK voltage level translation architecture

When  $V_{CCB\_EN} = 0$  then CTL =  $V_{CCB}$  and line is high-Z.

When  $V_{CCB\_EN} = 1$  then CTL = GND and line is active.

Figure 3. IO voltage level translation architecture

When  $V_{CCB\_EN} = 0$  then CTL = VCCB and line is high-Z.

When  $V_{CCB} = 1$  then CTL = GND and line is active.

#### **EMI** filter

All input/output driver stages are equipped with EMI filters to reduce interferences towards sensitive mobile communication.

#### **ESD** protection

The device has robust ESD protections on all SIM card pins as well as on the V<sub>CCB</sub> pin. The architecture prevents any stress for the host: the voltage translator discharges any stress to supply ground.

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                       | Parameter                                                                       | Condition                                                  | าร                   | Min.      | Max.                  | Unit |

|------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|-----------|-----------------------|------|

| Vcca                         | Host supply voltage                                                             |                                                            |                      | GND - 0.5 | 2.4                   | V    |

| V <sub>CCB</sub>             | SIM supply voltage                                                              |                                                            |                      | GND - 0.5 | 4.0                   | V    |

| V <sub>I</sub><br>(CLK_HOST) | Input voltage on pin<br>CLK_HOST                                                | Input signal voltage                                       | , HOST side          | GND - 0.5 | V <sub>CCA</sub> +0.3 | ٧    |

| V <sub>I</sub><br>(RST_HOST) | Input voltage on pin<br>RST_HOST                                                | Input signal voltage                                       | , HOST side          | GND - 0.5 | V <sub>CCA</sub> +0.3 | ٧    |

| V <sub>I</sub><br>(IO_HOST)  | Input voltage on pin IO_HOST                                                    | Input signal voltage                                       | , HOST side          | GND - 0.5 | V <sub>CCA</sub> +0.3 | V    |

| V <sub>I</sub><br>(EN)       | Input voltage on pin<br>EN                                                      | Enable input voltage                                       | , HOST side          | GND - 0.5 | 2.4                   | >    |

| Vı<br>(CLK_SIM)              | Input voltage on pin<br>CLK_SIM                                                 | Input signal voltage                                       | e, SIM side          | GND - 0.5 | V <sub>CCB</sub> +0.3 | ٧    |

| V <sub>I</sub><br>(RST_SIM)  | Input voltage on pin<br>RST_SIM                                                 | Input signal voltage, SIM side                             |                      | GND - 0.5 | V <sub>CCB</sub> +0.3 | ٧    |

| V <sub>I</sub><br>(IO_SIM)   | Input voltage on pin IO_SIM                                                     | Input signal voltage, SIM side                             |                      | GND - 0.5 | V <sub>CCB</sub> +0.3 | V    |

| TstG                         | Storage temperature                                                             |                                                            |                      | -65       | +150                  | °C   |

| TJ                           | Junction temperature                                                            |                                                            |                      | -40       | +150                  | °C   |

| T <sub>A</sub>               | Ambient temperature                                                             |                                                            |                      | -40       | +85                   | °C   |

|                              |                                                                                 | IEC 61000-4-2,<br>level 4, all memory                      | Contact<br>discharge | -8        | +8                    | kV   |

| V                            | Electrostatic card- side pins, Air discharge V <sub>CCB</sub> and GND discharge |                                                            | -15                  | +15       | kV                    |      |

| V <sub>ESD</sub>             | voltage                                                                         | Human Body Mod<br>JEDEC JESD22-A1                          | ,                    | -2000     | +2000                 | ٧    |

|                              |                                                                                 | Charge Device Model (CDM)  JEDEC JESD22-C101E; all pins    |                      | -500      | +500                  | ٧    |

| ILU (IO)                     | Input/output<br>latch-up current                                                | JESD 78I<br>-0.5xV <sub>CC</sub> <v<sub>I&lt;1.5xV</v<sub> |                      | -200      | +200                  | mA   |

**Note:** All system level tests are performed with the application-specific capacitors connected to the supply pins  $V_{SUPPLY}$ ,  $V_{LDO}$  and  $V_{CCA}$ .

# ET4557

# **Electrical Characteristics**

$1.62 \text{ V} \le \text{V}_{\text{CCB}} \le 3.6 \text{ V}, \ 1.08 \text{ V} \le \text{V}_{\text{CCA}} \le 1.98 \text{ V}, \ \text{T}_{\text{A}} = -40 \ ^{\circ}\text{C} \ \text{to} \ +85 \ ^{\circ}\text{C}.$

| Symbol               | Parameter                        | Conditions                                                                 | Min.                      | Typ.(3) | Max.                  | Unit |  |

|----------------------|----------------------------------|----------------------------------------------------------------------------|---------------------------|---------|-----------------------|------|--|

| Basic Ope            | ration                           |                                                                            |                           | •       |                       |      |  |

| $V_{CCA}$            | Supply voltage <sup>(4)</sup>    |                                                                            | 1.08                      |         | 1.98                  | V    |  |

| I <sub>CCA</sub>     |                                  | Operating mode;<br>EN = V <sub>CCA</sub><br>f <sub>CLK_HOST</sub> = 1 MHz, |                           | 5       | 10                    | μA   |  |

|                      | Supply<br>current                | Quiescent current; EN and IO_HOST = V <sub>CCA</sub> , CLK_HOST = GND      |                           | 0.01    | 1                     | μA   |  |

|                      |                                  | Shutdown mode;<br>EN = GND                                                 |                           |         | 1                     | μA   |  |

| Vccв                 | SIM supply voltage               |                                                                            | 1.62                      |         | 3.6                   | V    |  |

| ICCB                 |                                  | Operating mode;<br>fcLK_HOST = 1 MHz,<br>EN= Vcca, Ci = 50 pF              |                           | 300     | 350                   | μA   |  |

|                      | SIM supply<br>current            | Quiescent current; EN and IO_HOST = V <sub>CCA</sub> , CLK_HOST = GND      |                           | 3.7     | 10                    | μA   |  |

|                      |                                  | Shutdown mode;<br>EN = GND                                                 |                           |         | 1                     | μA   |  |

|                      |                                  | host side                                                                  | -0.3                      |         | V <sub>CCA</sub> +0.3 |      |  |

| Vı                   | Input voltage                    | Sim card side                                                              | -0.3                      |         | V <sub>CCB</sub> +0.3 | V    |  |

| Automatic            | Enable Feature: V <sub>CCB</sub> |                                                                            |                           | I       |                       |      |  |

| V <sub>CCB_EN</sub>  | Device enable voltage level      | V <sub>CCA</sub> ≥ 1.0 V,<br>V <sub>CCB</sub> rising edge                  | 1.62                      |         |                       | V    |  |

| V <sub>CCB_DIS</sub> | Device disable voltage level     | V <sub>CCA</sub> ≥ 1.0 V,<br>V <sub>CCB</sub> falling edge                 |                           |         | 0.80                  | V    |  |

| Hardware             | Enable Pin                       |                                                                            |                           |         |                       |      |  |

| Vıн                  | HIGH-level input voltage         | 1.08 V ≤ V <sub>CCA</sub> < 1.98 V<br>EN pin threshold                     | 0.65×<br>V <sub>CCA</sub> |         |                       | V    |  |

| VIL                  | LOW-level input voltage          | 1.08 V ≤ V <sub>CCA</sub> < 1.98 V<br>EN pin threshold                     |                           |         | 0.35×<br>Vcca         | V    |  |

| Level Shift          | ter                              |                                                                            |                           | 1       | ı                     |      |  |

| V <sub>IH</sub> (6)  | HIGH-level                       | IO_HOST, RST_HOST,<br>CLK_HOST<br>1.08 V ≤ V <sub>CCA</sub> < 1.98 V       | 0.65×<br>Vcca             |         | Vcca+0.3              | V    |  |

|                      | input voltage                    | IO_SIM                                                                     | 0.65×<br>V <sub>ССВ</sub> |         | V <sub>ССВ</sub> +0.3 | V    |  |

# ET4557

# **Electrical Characteristics(Continued)**

1.62 V  $\leq$  V\_CCB  $\leq$  3.6 V, 1.08 V  $\leq$  V\_CCA  $\leq$  1.98 V,  $T_A$  = -40 °C to +85 °C.

| Symbol              | Parameter                                   | Conditions                                                   | Min.                      | Тур. | Max.                              | Unit |

|---------------------|---------------------------------------------|--------------------------------------------------------------|---------------------------|------|-----------------------------------|------|

| V <sub>IL</sub> (6) | LOW-level                                   | IO_HOST, RST_HOST,<br>CLK_HOST                               | -0.15                     |      | 0.35×<br>Vcca                     | V    |

| VIL                 | input voltage                               | IO_SIM                                                       | -0.15                     |      | 0.35 <b>х</b><br>V <sub>ССВ</sub> | V    |

|                     |                                             | IO_SIM connected to VCCB,VCCB=2.8V                           | 5                         | 6    | 7.7                               | kΩ   |

| R <sub>PU</sub>     | Pull-up<br>resistance                       | IO_SIM connected to V <sub>CCB</sub> ,V <sub>CCB</sub> =1.8V | 5.5                       | 7    | 9.5                               | kΩ   |

|                     |                                             | IO_HOST connected to V <sub>CCA</sub>                        | 3.3                       | 4.3  | 6                                 | kΩ   |

|                     |                                             | RST_SIM, CLK_SIM;<br>I <sub>OH</sub> = -1 mA                 | 0.85×<br>V <sub>CCB</sub> |      | Vccв                              | V    |

| Vон                 | HIGH-level<br>output voltage                | IO_SIM;<br>I <sub>OH</sub> = -20 μA                          | 0.85×<br>V <sub>ССВ</sub> |      | Vccв                              | V    |

|                     |                                             | IO_HOST;<br>Iοн = -20 μA                                     | 0.85×<br>V <sub>CCA</sub> |      | Vcca                              | V    |

|                     | LOW-level<br>output voltage                 | RST_SIM, CLK_SIM;<br>I <sub>OL</sub> = 1 mA                  | 0                         |      | 0.115×<br>V <sub>ССВ</sub>        | mV   |

| $V_{OL}$            |                                             | IO_SIM; I <sub>OL</sub> = 1 mA                               | 0                         |      | 0.125×<br>V <sub>ССВ</sub>        | mV   |

|                     |                                             | IO_HOST; I <sub>OL</sub> = 1 mA                              | 0                         |      | 0.16 <b>x</b><br>V <sub>CCA</sub> | mV   |

| R <sub>PD</sub>     | Pull-down<br>resistance                     | CLK_HOST/SIM,<br>RST_HOST/SIM;<br>EN = 0                     | 70                        | 100  | 130                               | kΩ   |

| EMI Filter          | •                                           |                                                              |                           |      |                                   |      |

|                     |                                             | IO_SIM;<br>R1 tolerance ± 30 %                               | -                         | 30   | -                                 | Ω    |

| Rs                  | Series resistance <sup>(7)</sup>            | RST_SIM;<br>R1 tolerance ± 30 %                              | -                         | 30   | -                                 | Ω    |

|                     |                                             | CLK_SIM;<br>R1 tolerance ± 30 %                              | -                         | 30   | -                                 | Ω    |

|                     | L                                           | IO_SIM                                                       | -                         | 8.5  | -                                 | pF   |

| Cio                 | Input/Output/<br>Capacitance <sup>(7)</sup> | RST_SIM                                                      | -                         | 8.5  | -                                 | pF   |

|                     |                                             | CLK_SIM                                                      | -                         | 8.5  | -                                 | pF   |

# **Electrical Characteristics(Continued)**

$1.62 \text{ V} \le \text{V}_{\text{CCB}} \le 3.6 \text{ V}, \ 1.08 \text{ V} \le \text{V}_{\text{CCA}} \le 1.98 \text{ V}, \ \text{T}_{\text{A}} = -40 \ ^{\circ}\text{C} \ \text{to} \ +85 \ ^{\circ}\text{C}.$

| Symbol                 | Parameter                                                                     | Conditions                                         | Min. | Тур. | Max. | Unit |  |  |  |

|------------------------|-------------------------------------------------------------------------------|----------------------------------------------------|------|------|------|------|--|--|--|

| Dynamic o              | Dynamic characteristics                                                       |                                                    |      |      |      |      |  |  |  |

|                        | $F_{CLK} = F_{IO} = 1$ MHz; unless otherwise specified. Refer to Figure 4;    |                                                    |      |      |      |      |  |  |  |

| $V_{CCA} = 1.8$        | $V; V_{CCB} = 3.0 V; SIM card C$                                              | L ≤ 30 pF; host C <sub>L</sub> ≤ 10 pF             |      |      | ı    | T    |  |  |  |

|                        | t <sub>PHL</sub> and t <sub>PLH</sub> are t <sub>PD</sub>                     | I/O channel; SIM card side to host side            |      | 8    | 15   | ns   |  |  |  |

| t <sub>PD</sub>        | propagation delay <sup>(7)</sup>                                              | all channels; host side to SIM card side           |      | 8    | 15   | ns   |  |  |  |

| t⊤                     | t <sub>THL</sub> and t <sub>TLH</sub> are the transition time. <sup>(7)</sup> |                                                    |      |      | 10   | ns   |  |  |  |

| tsk(o)                 | Output skew time <sup>(5) (7)</sup> between channels; 1O_SIM and CLK_SIM      |                                                    | 2    |      | ns   |      |  |  |  |

| Fclk                   | Clock frequency <sup>(7)</sup>                                                | CLK_SIM                                            |      |      | 10   | MHz  |  |  |  |

| V <sub>CCA</sub> = 1.2 | V; V <sub>CCB</sub> = 1.8 V; SIM card                                         | C <sub>L</sub> ≤ 30 pF; host C <sub>L</sub> ≤ 10 p | F    |      |      |      |  |  |  |

| taa                    | t <sub>PHL</sub> and t <sub>PLH</sub> are t <sub>PD</sub>                     | I/O channel; SIM card side to host side            |      | 15   | 25   | ns   |  |  |  |

| t <sub>PD</sub>        | propagation delay <sup>(5)</sup>                                              | all channels; host side to SIM card side           |      | 15   | 25   | ns   |  |  |  |

| t⊤                     | t <sub>THL</sub> and t <sub>TLH</sub> are the transition time. <sup>(5)</sup> |                                                    |      |      | 10   | ns   |  |  |  |

| tsk(o)                 | Output skew time <sup>(5)(7)</sup>                                            | between channels; IO_SIM and CLK_SIM               |      | 2    |      | ns   |  |  |  |

| F <sub>CLK</sub>       | Clock frequency <sup>(7)</sup>                                                | CLK_SIM                                            |      |      | 10   | MHz  |  |  |  |

### Notes:

- 3) Typical values measured at 25 °C

- 4) The voltage must not exceed 1.98 V steady state.

- 5) Skew between any two outputs of the same package switching in the same direction with same C<sub>L</sub>.

- **6)** V<sub>IL</sub>, V<sub>IH</sub> depend on the individual supply voltage per interface

- 7) Guaranteed by design Note: This parameter is guaranteed by design and characterization.

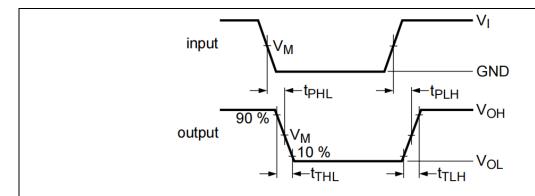

Figure 4. Data Input to Data Output Propagation Delay Times

Measurement points are given in EC table.

Vol and Voh are typical output voltage levels that occur with the output load.

t<sub>PHL</sub> and t<sub>PLH</sub> are t<sub>PD</sub> propagation delay; t<sub>THL</sub> and t<sub>TLH</sub> are the transition time.

• This electric circuit only supplies for reference.

# **Application Circuits**

#### Input/output capacitor considerations

It is recommended that a 1µF and 100nF capacitors having low Equivalent Series Resistance (ESR) are used respectively at  $V_{CCA}$  and  $V_{CCB}$  input terminals of the device. X5R and X7R type multi-layer ceramic capacitors (MLCC) are preferred because they have minimal variation in value and ESR over temperature. The maximum ESR should be <  $500m\Omega$  ( $50m\Omega$  typical).

#### Layout consideration

The capacitors should be placed directly at the terminals and ground plane. It is recommended to design the PCB so that the V<sub>CCA</sub> and V<sub>CCB</sub> pins are bypassed with a capacitor with each ground returning to a common node at the GND pin of the device such that ground loops are minimized.

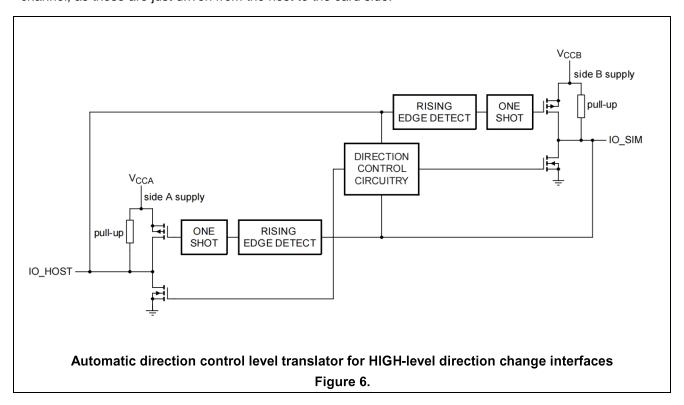

#### Level translator stage

The architecture of the device I/O channel is shown in Figure 6. The device does not require an extra input signal to control the direction of data flow from host to SIM or from SIM to host.

As a change of driving direction is just possible when both sides are in HIGH state, the control logic is recognizing the first falling edge granting it control about the other signal side.

During a rising edge signal, the non-driving output is driven by a one- shot circuit to accelerate the rising edge. In case of a communication error or some other unforeseen incident that would drive both connected sides to be drivers at the same time, the internal logic automatically prevents stuck-at situation, so both I/Os will return to HIGH level once released from being driven LOW.

The channels RST and CLK just contain single direction drivers without the holding mechanism of the I/O channel, as these are just driven from the host to the card side.

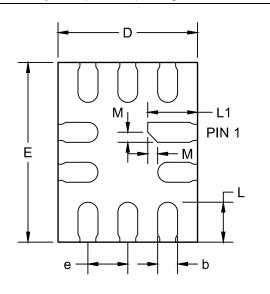

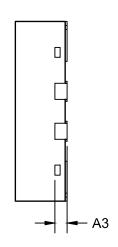

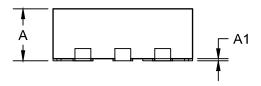

# **Package Dimension**

QFN10: plastic, extremely thin quad flat package; no leads; 10 terminals;

# COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN     | NOM         | MAX   |  |

|--------|---------|-------------|-------|--|

| Α      | 0.500   | 0.550       | 0.600 |  |

| A1     | 0.000   | 0.020       | 0.050 |  |

| A3     |         | 0.127REF    |       |  |

| b      | 0.150   | 0.200       | 0.250 |  |

| D      | 1.350   | 1.400       | 1.450 |  |

| Е      | 1.750   | 1.750 1.800 |       |  |

| е      | 0.300   | 0.400       | 0.500 |  |

| L      | 0.350   | 0.400       | 0.450 |  |

| L1     | 0.450   | 0.500       | 0.550 |  |

| М      | 0.01REF |             |       |  |

Unit: mm

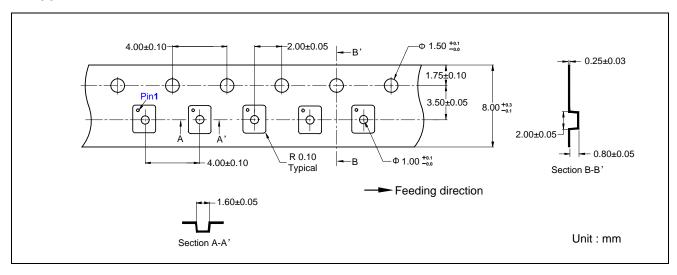

# Reel

# **Revision History and Checking Table**

| Version | Date       | Revision Item                                   | Modifier     | Function & Spec<br>Checking | Package & Tape<br>Checking |

|---------|------------|-------------------------------------------------|--------------|-----------------------------|----------------------------|

| 0.0     | 2022.5.9   | Preliminary Version                             | You-Yingquan | Liu Kangsheng               | Liujy                      |

| 0.2     | 2022.11.9  | Update Typesetting                              | Shi Bo       | Liu Kangsheng               | Liujy                      |

| 0.3     | 2023.2.9   | Electrical parameter update                     | Shi Bo       | Liu Kangsheng               | Liujy                      |

| 0.4     | 2023.4.6   | Electrical parameter update                     | Zou Chaomin  | Liu Kangsheng               | Liujy                      |

| 1.0     | 2023.5.4   | Electrical parameter update                     | Zou Chaomin  | Liu Kangsheng               | Liujy                      |

| 1.1     | 2023.5.19  | Electrical parameter update                     | Zou Chaomin  | Liu Kangsheng               | Liujy                      |

| 1.2     | 2023.5.25  | Add reel and marking                            | Shibo        | Liu Kangsheng               | Liujy                      |

| 1.3     | 2023.11.29 | Update package Dimension                        | Shibo        | Liu Kangsheng               | Liujy                      |

| 1.4     | 2025.09.20 | Update V <sub>OL</sub> and Package<br>Dimension | Wuhs         | Liu Kangsheng               | Liujy                      |