### ET3166 - 6 CH Load Switch with I<sup>2</sup>C Control

### **General Description**

The ET3166 is CMOS-based 6 channels integrated load switch with I<sup>2</sup>C Control. Load switch 1 to 6 contains P-Channel MOSFET that can operate over an input voltage of 1.2V to 5.5V and supports a maximum continuous current of 2A.

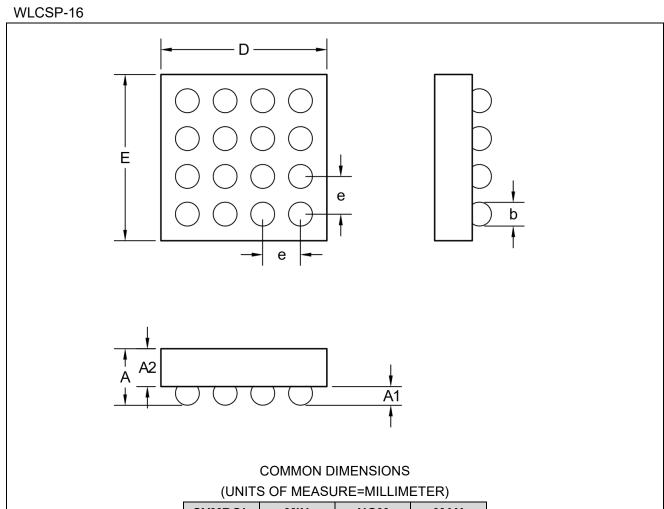

The ET3166 is available in small package: WLCSP16 (1.54mm×1.54mm,0.35mm pitch).

### **Features**

- Load switch 1 to 6 input voltage operating range: 1.2V to 5.5V

- Load switch 1 to 6 typical R<sub>DS(ON)</sub>:

- $52m\Omega$  at  $V_{INX} = 5V$

- $120m\Omega$  at  $V_{INX} = 1.8V$

- V<sub>SYS</sub> input voltage operation range: 1.6V to 5.5V

- I2C serial control to program each load switch on/off

- Part No. and package

| Part No. | Package                             | MSL     |

|----------|-------------------------------------|---------|

| ET3166   | WLCSP16 (1.54×1.54mm,0.35mm pitch ) | Level 1 |

### **Applications**

- Constant-voltage power supply for battery-powered device

- Constant-voltage power supply for smartphones, tables

- Constant-voltage power supply for cameras, DVRs, STB and camcorders

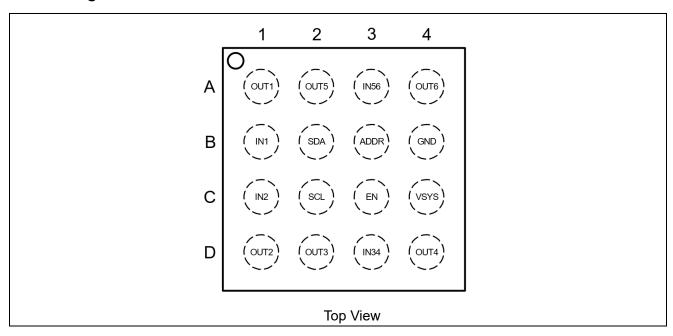

## **Pin Configuration**

### **Pin Function**

| Pin No. | Pin Name | Pin Function                                                                                                 |  |  |

|---------|----------|--------------------------------------------------------------------------------------------------------------|--|--|

| A1      | OUT1     | Load switch 1 output.                                                                                        |  |  |

| A2      | OUT5     | Load switch 5 output.                                                                                        |  |  |

| A3      | IN56     | Load switch 5 and 6 supply input.                                                                            |  |  |

| A4      | OUT6     | Load switch 6 output.                                                                                        |  |  |

| B1      | IN1      | Load switch 1 supply input.                                                                                  |  |  |

| B2      | SDA      | I <sup>2</sup> C interface.                                                                                  |  |  |

| В3      | ADDR     | I <sup>2</sup> C address set pin.                                                                            |  |  |

| B4      | GND      | Ground pin.                                                                                                  |  |  |

| C1      | IN2      | Load switch 2 supply input.                                                                                  |  |  |

| C2      | SCL      | I <sup>2</sup> C interface.                                                                                  |  |  |

| C3      | EN       | Load switch output Enable(active high), Device will reset all registers to default value when EN pin is low. |  |  |

| C4      | VSYS     | System Supply input.                                                                                         |  |  |

| D1      | OUT2     | Load switch 2 output.                                                                                        |  |  |

| D2      | OUT3     | Load switch 3 output.                                                                                        |  |  |

| D3      | IN34     | Load switch 3 and 4 supply input.                                                                            |  |  |

| D4      | OUT4     | Load switch 4 output.                                                                                        |  |  |

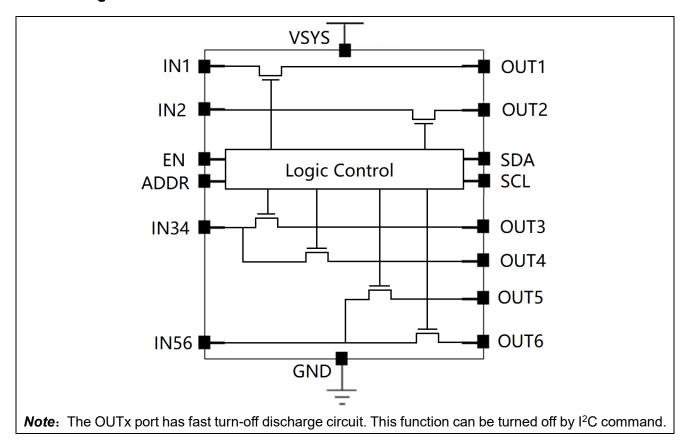

### **Block Diagram**

### **Functional Description**

ET3166 has 6 channels load switch. Load switch 1 to 6 are using PMOSFET.

### **Startup**

The ET3166 LDSW's can be enabled two ways using the I<sup>2</sup>C register bits if EN is high.

- 1. Setting LDSWX\_SEQ = 000 in 0x05(LDSW12\_SEQ) or 0x06(LDSW34\_SEQ) or 0x07(LDSW56\_SEQ) and the LDSWX\_EN assigned to the LDSW in register, ENABLE to 1.

- 2. Setting LDSWX\_SEQ > 000 in registers and then set seq\_ctrl[1:0] = 2'b01 in SEQ\_CTR register.

Power-up and shut down of each regulator can be controlled by an I<sup>2</sup>C register. It can be set at the registers Idswx\_seq[2:0] (x=1 to 7) respectively. Idswx\_en is an internal signal to enable one of regulators, if Idsw\_seq[2:0] set to '000', that LDSWX channel can be controlled directly by a bit specified in register LDSW\_EN.

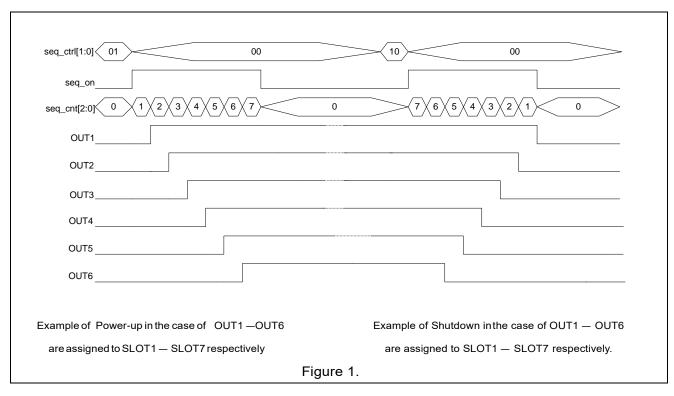

3. Automatic Power Up/Down Sequence Control

ET3166 has seven SLOTs to which each regulator can be assigned;

They are started by seq\_ctrl[1:0] signal. when seq\_ctrl[1:0] is set '01'. Internal counter seq\_cnt[2:0] starts increments from 0 ("000") to 7 ("111"). When seq\_ctrl[1:0] is set '10', seq\_cnt[2:0] decrements from 7 ("111") to 0 ("000"). Regulators assigned to one of SLOTs starts power-up or power-down.

The seq\_cnt[2:0] matches the SLOT number, when seq\_cnt[2:0]=000, it indicates that sequencing has completed or not started.

Internal logic signal seq\_on=1 indicates that sequencing is executing and somewhere between the start of slot1 and the end of slot7, seq\_on=0, it indicates that has completed or not started.

#### 4. EN Pin Control

When EN pin is in low level, the IC is shut down, all internal circuits are off, and all the parts draw very little current. In this state, all the registers will be reset to their default value, and I<sup>2</sup>C cannot be written to or read.

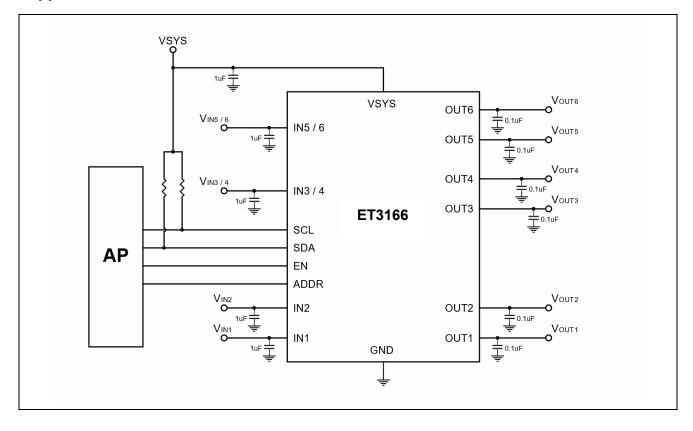

#### **Input and output Capacitor**

To limit the voltage drop on the input supply caused by transient inrush current when the switch turns on into a discharged load capacitor or short-circuit, a capacitor must be placed between the  $V_{INX}$  and GND pins. A 1 $\mu$ F ceramic capacitor,  $C_{INX}$ , placed close to the pins is usually sufficient. Higher-value  $C_{INX}$  can be used to reduce the voltage drop in higher-current applications.

A  $0.1\mu F$  capacitor,  $C_{OUTX}$ , should be placed between the  $V_{OUTX}$  and GND pins. This capacitor prevents parasitic board inductance from forcing  $V_{OUTX}$  below GND when the switch is on.  $C_{INX}$  greater than  $C_{OUTX}$  is highly recommended.  $C_{OUTX}$  greater than  $C_{IN}$  can cause  $V_{OUTX}$  to exceed  $V_{INX}$  when the system supply is removed. This could result in current flow through the body diode from  $V_{OUTX}$  to  $V_{INX}$ .

Recommended C<sub>VSYS</sub>=1.0uF or greater.

#### **Auto Discharging**

For each channel, when shut down the output, the Auto-Discharging circuit will be turned on to discharge the electric charge on output capacitor, and decrease the voltage of output pin in very short time. The Auto-Discharging function is optional. Set related bits to select output discharge function for Discharge

Resistor (LDSW DIS Register), "0": Disable. "1": Enable.

#### **RCB** function

ET3166 has a true Reverse Current function that obstructs unwanted reverse current from OUTx to INx during both ON and OFF states. The RCB function can be set by I<sup>2</sup>C instruction(LDSW\_RCB register).

| LSWx state | ldswx_rcb | RCB function |

|------------|-----------|--------------|

| OFF        | 0         | Υ            |

| OFF        | 1         | Υ            |

| ON         | 0         | N            |

| ON         | 1         | Y            |

**Note:** x is 1~6.

LSWx state is controlled by EN pin or LDSW\_EN Register.

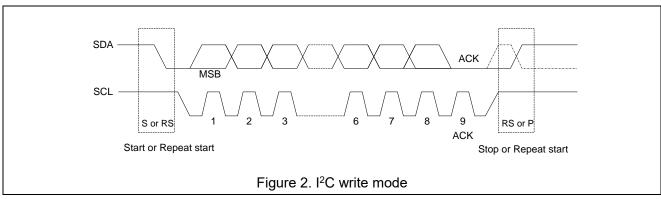

### Serial Port Interface (I<sup>2</sup>C)

#### Bus Interface

Baseband Processor can transmit data with ET3166 each other through SDA and SCL port. SDA and SCL composite bus interface, and a pull-up resistor to the power supply should be connected.

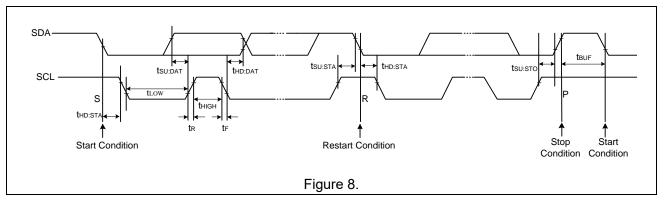

### **Data Validity**

When the SCL signal is high, the data of SDA port is valid and stable. Only when the SCL signal is low, the level on the SDA port can be changed.

### Start (Re-start) and Stop Working Conditions

When the SCL signal is high, SDA signal from high to low represents start or re-start working conditions, while the SCL signal is high, SDA signal from low to high represents stop working conditions.

#### Byte format

Each byte of data line contains 8 bits, which contains an acknowledge bit. The first data is transmitted MSB.

#### Acknowledge

During the writing mode, ET3166 will send a low level response signal with one period width to the SDA port. During the reading mode, ET3166 will not send response signal and the host will send a high response signal one period width to the SDA.

ACK=Acknowledge

MSB=Most Significant Bit

S=Start Conditions RS=Restart Conditions P=Stop Conditions

Fastest Transmission Speed =400kHz

Restart: SDA-level turnover as expressed by the dashed line waveform

### 7bit Chip Address:

| Address  | ADDR Pin Set         |

|----------|----------------------|

| 0011000b | ADDR connect to GND  |

| 0011001b | ADDR connect to VSYS |

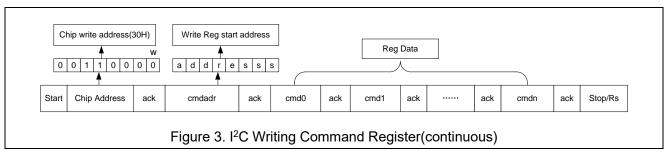

### **PC Writing Command Register Interface Protocol (continuous):**

ACK=Acknowledge

Start=Start Conditions

Chip address=Write register address =0011000+0(w)b

ack=Acknowledge

Write Reg start address byte = cmdadr(x+ REG's 7bit address)

ack=Acknowledge

Reg data 0 = cmd0(Command data0)

ack=Acknowledge

.....

Reg data n =cmdn(Command datan)

ack=Acknowledge

Stop/Rs=Stop Condition/Restart Condition

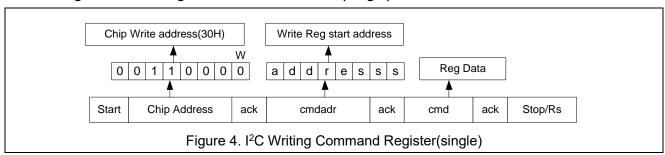

### PC Writing Command Register Interface Protocol (single):

Start=Start Conditions

Chip address = Write register address = 0011000+0(w)b

ack=Acknowledge

Write Reg start address byte = cmdadr(x + REG's 7bit address)

ack=Acknowledge

Reg data= cmd(Command data)

ack=Acknowledge

Stop/Rs=Stop Condition/Restart Condition

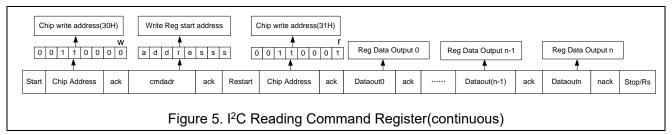

### **PC** Reading Command Register Interface Protocol (continuous)

Start=Start Conditions

Chip address =Write register address=0011000+0(w)b

ack=Acknowledge from ET3166

Write Reg start address byte = cmdadr(x + REG's 7bit address)

ack=Acknowledge from ET3166

Restart=Restart condition

Chip address Read register address=0011000+1(r)b

ack=Acknowledge from ET3166

Dataout0=Register data output 0

ack=Acknowledge from Host

.....

Dataoutn=Register data output n

nack=No Acknowledge from Host

Stop/Rs=Stop Condition/Restart Condition

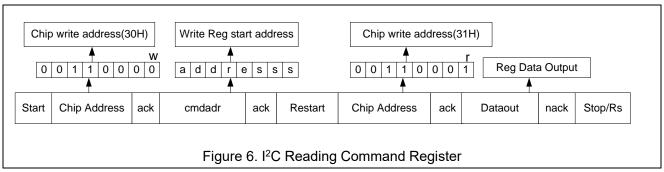

### **PC** Reading Command Register Interface Protocol (single)

Start=Start Conditions

Chip address =Write register address=0011000+0(w)b

ack=Acknowledge from ET3166

Write Reg start address byte = cmdadr(x + REG's 7bit address)

ack=Acknowledge from ET3166

Restart=Restart condition

Chip address Read register address=0011000+1(r)b

ack=Acknowledge from ET3166

Dataout=Register data output

nack=No Acknowledge from Host

Stop/Rs=Stop Condition/Restart Condition

### **Register Map**

| Addr | Name        | RST  | Bit7   | Bit6     | Bit5               | Bit4              | Bit3               | Bit2              | Bit1           | Bit0      |  |

|------|-------------|------|--------|----------|--------------------|-------------------|--------------------|-------------------|----------------|-----------|--|

| 0x00 | CHIPID      | 0x30 |        |          |                    | 001100            |                    |                   | chip_id[1:0]   |           |  |

| 0x01 | VERID       | 0x00 |        |          |                    | 000000            |                    |                   | ver_id[1:0]    |           |  |

| 0x02 | LDSW_EN     | 0x00 | 0      | 0        | ldsw6_en           | ldsw5_en          | ldsw4_en           | ldsw3_en          | ldsw2_en       | ldsw1_en  |  |

| 0x03 | LDSW_DIS    | 0x3F | 0      | 0        | ldsw6_dis          | ldsw5_dis         | ldsw4_dis          | ldsw3_dis         | ldsw2_dis      | ldsw1_dis |  |

| 0x04 | LDSW_TR0    | 0x00 | 0      | 0        | ldsw6_tr0          | ldsw5_tr0         | ldsw4_tr0          | ldsw3_tr0         | ldsw2_tr0      | ldsw1_tr0 |  |

| 0x05 | LDSW12_SEQ  | 0x00 | 0      | 0        | 0   ldsw2_seq[2:0] |                   |                    |                   | ldsw1_seq[2:0] |           |  |

| 0x06 | LDSW34_SEQ  | 0x00 | 0      | 0        |                    | ldsw4_seq[2:0]    |                    |                   | ldsw3_seq[2:0] |           |  |

| 0x07 | LDSW56_SEQ  | 0x00 | 0      | 0        |                    | ldsw6_seq[2:0]    |                    |                   | ldsw5_seq[2:0] |           |  |

| 0x08 | SEQ_CTR     | 0x00 | seq_sp | eed[1:0] | seq_c              | trl[1:0]          | seq_on             |                   | seq_cnt[2:0]   |           |  |

| 0x09 | LDSW_TR1    | 0x00 | 0      | 0        | ldsw6_tr1          | ldsw5_tr1         | ldsw4_tr1          | ldsw3_tr1         | ldsw2_tr1      | ldsw1_tr1 |  |

| 0x0A | LDSW_RCB    | 0x00 | 0      | 0        | ldsw6_rcb          | ldsw5_rcb         | ldsw4_rcb          | ldsw3_rcb         | ldsw2_rcb      | ldsw1_rcb |  |

| 0x0B | LDSW_STA    | 0x00 | 0      | 0        | ldsw6_sta          | ldsw5_sta         | ldsw4_sta          | ldsw3_sta         | ldsw2_sta      | ldsw1_sta |  |

| 0x69 | SOFTRST_CTR | 0x00 |        | V        | Vrite B0H to this  | s register can re | eset all the regis | sters to their de | fault value    |           |  |

Note: Rev.—Reserve, keep "0".

#### Register description

0x00 CHIPID Register---- Indicates the product ID with revision. Default = 0x30

chip\_id[1:0] Indicates the product ID with revision. Read only.

### 0x01 VERID Register---- Indicates the device ID with revision. Default = 0x00

ver\_id[1:0] Indicates the device ID with revision. Read only.

### 0x02 LDSW\_EN Register ----LDSWs enable control register. Default = 0x00

Load Switch enable control register by I<sup>2</sup>C while the register value of ldswx\_seq[2:0] are set to be default "000". This register can be written to enable or disable the corresponding LDSW regulator.

| Bit | Name     | Default | Type | Description                                 |

|-----|----------|---------|------|---------------------------------------------|

| 7   | Rev.     | 0       | R    | Reserved                                    |

| 6   | Rev.     | 0       | R    | Reserved                                    |

| 5   | ldsw6_en | 0       | R/W  | LDSW6 enable control: 0b:Disable 1b: Enable |

| 4   | ldsw5_en | 0       | R/W  | LDSW5 enable control: 0b:Disable 1b: Enable |

| 3   | ldsw4_en | 0       | R/W  | LDSW4 enable control: 0b:Disable 1b: Enable |

| 2 | ldsw3_en | 0 | R/W | LDSW3 enable control: 0b:Disable | 1b: Enable |

|---|----------|---|-----|----------------------------------|------------|

| 1 | ldsw2_en | 0 | R/W | LDSW2 enable control: 0b:Disable | 1b: Enable |

| 0 | ldsw1_en | 0 | R/W | LDSW1 enable control: 0b:Disable | 1b: Enable |

### 0x03 LDSW\_DIS Register ---- Discharge Resistor Selection. Default = 0x3F

Each LDSW regulators output discharge resistor enable control.

| Bit | Name        | Default | Туре                                                  | Description                                                    |

|-----|-------------|---------|-------------------------------------------------------|----------------------------------------------------------------|

| 7   | Rev.        | 0       | R                                                     | Reserved                                                       |

| 6   | Rev.        | 0       | R                                                     | Reserved                                                       |

|     |             |         |                                                       | LDSW6 Discharge Enabled/Disabled control :                     |

|     |             |         |                                                       | 0b: Disable                                                    |

|     |             |         |                                                       | Pull down will not be activated when LDSW6 is disabled by any  |

| 5   | ldsw6_dis   | 1       | R/W                                                   | event                                                          |

|     |             |         |                                                       | 1b: Enable                                                     |

|     |             |         |                                                       | Pull down will be activated when LDSW6 is disabled by          |

|     |             |         |                                                       | EN going low or ldsw6_en=0 or a Sequenced shutdown             |

|     |             |         |                                                       | LDSW5 Discharge Enabled/Disabled control :                     |

|     |             |         |                                                       | 0b: Disable                                                    |

|     |             |         |                                                       | Pull down will not be activated when LDSW5 is disabled by any  |

| 4   | ldsw5_dis   | 1       | R/W                                                   | event                                                          |

|     |             |         |                                                       | 1b: Enable                                                     |

|     |             |         | Pull down will be activated when LDSW5 is disabled by |                                                                |

|     |             |         |                                                       | EN going low or ldsw5_en=0 or a Sequenced shutdown             |

|     |             |         |                                                       | LDSW4 Discharge Enabled/Disabled control :                     |

|     |             |         |                                                       | 0b: Disable                                                    |

|     |             |         |                                                       | Pull down will not be activated when LDSW4 is disabled by any  |

| 3   | ldsw4_dis   | 1       | R/W                                                   | event                                                          |

|     |             |         |                                                       | 1b: Enable                                                     |

|     |             |         |                                                       | Pull down will be activated when LDSW4 is disabled by EN going |

|     |             |         |                                                       | low or ldsw4_en=0 or a Sequenced shutdown                      |

|     |             |         |                                                       | LDSW3 Discharge Enabled/Disabled control :                     |

|     |             |         |                                                       | 0b: Disable                                                    |

|     |             |         |                                                       | Pull down will not be activated when LDSW3 is disabled by any  |

| 2   | ldsw3_dis   | 1       | R/W                                                   | event                                                          |

|     |             |         |                                                       | 1b: Enable                                                     |

|     |             |         |                                                       | Pull down will be activated when LDSW3 is disabled by          |

|     |             |         |                                                       | EN going low or ldsw3_en=0 or a Sequenced shutdown             |

|     |             |         |                                                       | LDSW2 Discharge Enabled/Disabled control :                     |

|     |             |         |                                                       | 0b: Disable                                                    |

| 1   | 1 Idsw2_dis | 1       | R/W                                                   | Pull down will not be activated when LDSW2 is disabled by any  |

|     |             |         |                                                       | event                                                          |

|     |             |         |                                                       | 1b: Enable                                                     |

|     |             |         |                                                       | Pull down will be activated when LDSW2 is disabled by          |

|   |           |   |     | EN going low or ldsw2_en=0 or a Sequenced shutdown            |

|---|-----------|---|-----|---------------------------------------------------------------|

|   |           |   |     | LDSW1 Discharge Enabled/Disabled control :                    |

|   |           |   |     | 0b: Disable                                                   |

|   |           |   |     | Pull down will not be activated when LDSW1 is disabled by any |

| 0 | ldsw1_dis | 1 | R/W | event                                                         |

|   |           |   |     | 1b: Enable                                                    |

|   |           |   |     | Pull down will be activated when LDSW1 is disabled by         |

|   |           |   |     | EN going low or ldsw1_en=0 or a Sequenced shutdown            |

# $0x04/09H\ LDSW_TR0/1\ Register$ ----Load Switch output voltage rise timing Selection. Default = 0x00

$V_{INX}$  =3.3V,  $R_L$ =150 $\Omega$ ,  $C_L$ =0.1 $\mu F$

| Bit | Name      | Default | Туре  | Description                                              |

|-----|-----------|---------|-------|----------------------------------------------------------|

| 7   | Rev.      | 00/00   | R     | Reserved                                                 |

| 6   | Rev.      | 00/00   | R     | Reserved                                                 |

|     |           |         |       | LDSW6 output voltage (from 10% to 90%) rise time setting |

| 5   | ldsw6_tr1 | 00      | R/W   | control:                                                 |

| 5   | ldsw6_tr0 | 00      | R/VV  | 00b: 340us 01b: 32us                                     |

|     |           |         |       | 10b: 150us 11b: 1000us                                   |

|     |           |         |       | LDSW5 output voltage (from 10% to 90%) rise time setting |

| 4   | ldsw5_tr1 | 00      | R/W   | control:                                                 |

| 4   | ldsw5_tr0 | 00      | R/VV  | 00b: 340us 01b: 32us                                     |

|     |           |         |       | 10b: 150us 11b: 1000us                                   |

|     |           |         |       | LDSW4 output voltage (from 10% to 90%) rise time setting |

| _   | ldsw4_tr1 | 00      | D 447 | control:                                                 |

| 3   | ldsw4_tr0 | 00      | R/W   | 00b: 340us 01b: 32us                                     |

|     |           |         |       | 10b: 150us 11b: 1000us                                   |

|     |           |         |       | LDSW3 output voltage (from 10% to 90%) rise time setting |

|     | ldsw3_tr1 | 00      | D 447 | control:                                                 |

| 2   | ldsw3_tr0 | 00      | R/W   | 00b: 340us 01b: 32us                                     |

|     |           |         |       | 10b: 150us 11b: 1000us                                   |

|     |           |         |       | LDSW2 output voltage (from 10% to 90%) rise time setting |

| 4   | ldsw2_tr1 | 00      | R/W   | control:                                                 |

| 1   | ldsw2_tr0 | 00      | R/VV  | 00b: 340us 01b: 32us                                     |

|     |           |         |       | 10b: 150us 11b: 1000us                                   |

|     |           |         |       | LDSW1 output voltage (from 10% to 90%) rise time setting |

|     | ldsw1_tr1 | 00      | R/W   | control:                                                 |

| 0   | ldsw1_tr0 | 00      | K/VV  | 00b: 340us 01b: 32us                                     |

|     |           |         |       | 10b: 150us 11b: 1000us                                   |

### 0x05 LDSW12\_SEQ Register ---- Power sequence setting register. Default = 0x00

Power sequence setting register. there are 7 time slots defined as following table. The power-up sequence is start from slot1 to slot7, and shut down start from slot7 to slot1. Power-up and shut down of LDSW1/2 regulator can be set at any one of the slots.

| Bit | Name           | Default | Туре |                      | Description                                      |  |

|-----|----------------|---------|------|----------------------|--------------------------------------------------|--|

| 7:6 | Rev.           | 00      | R    | Reserved             |                                                  |  |

|     |                |         |      | LDSW2 Control select | table                                            |  |

|     |                |         |      | ldsw2_seq[2:0]       | VOUT2                                            |  |

|     |                |         |      | 000                  | Controlled by I <sup>2</sup> C register Idsw2_en |  |

|     |                |         |      | 001                  | Slot1                                            |  |

|     |                |         |      | 010                  | Slot2                                            |  |

| 5:3 | ldsw2_seq[2:0] | 000     | R/W  | 011                  | Slot3                                            |  |

|     |                |         |      | 100                  | Slot4                                            |  |

|     |                |         |      | 101                  | Slot5                                            |  |

|     |                |         |      | 110                  | Slot6                                            |  |

|     |                |         |      | 111                  | Slot7                                            |  |

|     |                |         |      | LDSW1 Control select | table                                            |  |

|     |                |         |      | ldsw1_seq[2:0]       | VOUT1                                            |  |

|     |                |         |      | 000                  | Controlled by I <sup>2</sup> C register Idsw1_en |  |

|     |                |         |      | 001                  | Slot1                                            |  |

|     |                |         |      | 010                  | Slot2                                            |  |

| 2:0 | ldsw1_seq[2:0] | 000     | R/W  | 011                  | Slot3                                            |  |

|     |                |         |      | 100                  | Slot4                                            |  |

|     |                |         |      | 101                  | Slot5                                            |  |

|     |                |         |      | 110                  | Slot6                                            |  |

|     |                |         |      | 111                  | Slot7                                            |  |

|     |                |         |      |                      |                                                  |  |

### 0x06 LDSW34\_SEQ Register ---- Power sequence setting register. Default = 0x00

Power sequence setting register. there are 7 time slots defined as following table. The power-up sequence is start from slot1 to slot7, and shut down start from slot7 to slot1. Power-up and shut down of each LDSW3/4 regulator can be set at any one of the slots.

| Bit | Name           | Default | Туре |                     | Description                                      |

|-----|----------------|---------|------|---------------------|--------------------------------------------------|

| 7:6 | Rev.           | 00      | R    | Reserved            |                                                  |

|     |                |         |      | LDSW4 Control selec | ct table                                         |

|     |                |         |      | ldsw4_seq[2:0]      | VOUT4                                            |

|     |                |         |      | 000                 | Controlled by I <sup>2</sup> C register Idsw4_en |

|     |                |         |      | 001                 | Slot1                                            |

|     |                |         |      | 010                 | Slot2                                            |

| 5:3 | ldsw4_seq[2:0] | 000     | R/W  | 011                 | Slot3                                            |

|     |                |         |      | 100                 | Slot4                                            |

|     |                |         |      | 101                 | Slot5                                            |

|     |                |         |      | 110                 | Slot6                                            |

|     |                |         |      | 111                 | Slot7                                            |

|     |                |         |      | LDSW3 Control selec | ct table                                         |

|     |                |         |      | ldsw3_seq[2:0]      | VOUT3                                            |

|     |                |         |      | 000                 | Controlled by I <sup>2</sup> C register Idsw3_en |

|     |                |         |      | 001                 | Slot1                                            |

|     |                |         |      | 010                 | Slot2                                            |

| 2:0 | ldsw3_seq[2:0] | 000     | R/W  | 011                 | Slot3                                            |

|     |                |         |      | 100                 | Slot4                                            |

|     |                |         |      | 101                 | Slot5                                            |

|     |                |         |      | 110                 | Slot6                                            |

|     |                |         |      | 111                 | Slot7                                            |

|     |                |         |      |                     |                                                  |

### 0x07 LDSW56\_SEQ Register ---- Power sequence setting register. Default = 0x00

Power sequence setting register. there are 7 time slots defined as following table. The power-up sequence is start from slot1 to slot7, and shut down start from slot7 to slot1. Power-up and shut down of each LDSW5/6 regulator can be set at any one of the slots.

| Bit | Name           | Default | Туре  | Description                |                                                  |  |  |  |

|-----|----------------|---------|-------|----------------------------|--------------------------------------------------|--|--|--|

| 7:6 | Rev.           | 00      | R     | Reserved                   |                                                  |  |  |  |

|     |                |         |       | LDSW6 Control select table |                                                  |  |  |  |

|     |                |         |       | ldsw6_seq[2:0]             | VOUT6                                            |  |  |  |

|     |                |         |       | 000                        | Controlled by I <sup>2</sup> C register Idsw6_en |  |  |  |

|     |                |         |       | 001                        | Slot1                                            |  |  |  |

|     |                |         | D 444 | 010                        | Slot2                                            |  |  |  |

| 5:3 | ldsw6_seq[2:0] | 000     | R/W   | 011                        | Slot3                                            |  |  |  |

|     |                |         |       | 100                        | Slot4                                            |  |  |  |

|     |                |         |       | 101                        | Slot5                                            |  |  |  |

|     |                |         |       | 110                        | Slot6                                            |  |  |  |

|     |                |         |       | 111                        | Slot7                                            |  |  |  |

|     |                |         |       | LDSW5 Control selec        | t table                                          |  |  |  |

|     |                |         |       | ldsw5_seq[2:0]             | VOUT5                                            |  |  |  |

|     |                |         |       | 000                        | Controlled by I <sup>2</sup> C register Idsw5_en |  |  |  |

|     |                |         |       | 001                        | Slot1                                            |  |  |  |

|     |                |         | D 444 | 010                        | Slot2                                            |  |  |  |

| 2:0 | ldsw5_seq[2:0] | 000     | R/W   | 011                        | Slot3                                            |  |  |  |

|     |                |         |       | 100                        | Slot4                                            |  |  |  |

|     |                |         |       | 101                        | Slot5                                            |  |  |  |

|     |                |         |       | 110                        | Slot6                                            |  |  |  |

|     |                |         |       | 111                        | Slot7                                            |  |  |  |

### 0x08 SEQ\_CTR Register ---- Power sequence setting and status register. Default = 0x00

| Bit | Name                 | Default | Туре | Description                          |                                  |  |  |

|-----|----------------------|---------|------|--------------------------------------|----------------------------------|--|--|

|     |                      |         |      | Define the slot period as following: |                                  |  |  |

|     |                      |         |      | Register Value                       | Slot period(ms)                  |  |  |

|     | 17.4 63              |         | 544  | 00                                   | 0.5                              |  |  |

| 7:6 | 7:6   seq_speed[1:0] | 00      | R/W  | 01                                   | 1.0                              |  |  |

|     |                      |         |      | 10                                   | 1.5                              |  |  |

|     |                      |         |      | 11                                   | 2.0                              |  |  |

|     |                      |         |      | Enables power-up or                  | r shut down of SEQ:              |  |  |

|     |                      |         |      | Register Value                       | Slot period(ms)                  |  |  |

| 5:4 | 000 otrl[1:0]        | 00      | W/C  | 00                                   | Default                          |  |  |

| 5.4 | seq_ctrl[1:0]        | 00      | W/C  | 01                                   | Starts an LDSW power up sequence |  |  |

|     |                      |         |      | 10                                   | Starts an LDSW shutdown sequence |  |  |

|     |                      |         |      | 11                                   | Bit configuration is ignored     |  |  |

13

|     |              |     |     | Note: The bits will always clear immediately when written to |                                                                                                                                                                                                                                                                            |  |  |  |

|-----|--------------|-----|-----|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|     |              |     |     | and always read back 00.                                     |                                                                                                                                                                                                                                                                            |  |  |  |

|     |              |     |     | Indicates the ac                                             | tivation signal of SEQ.                                                                                                                                                                                                                                                    |  |  |  |

|     |              |     |     | 0b: Indicates that                                           | at the sequencing is not in process                                                                                                                                                                                                                                        |  |  |  |

| 3   | cog on       | 0   | R   | 1b: Indicates that                                           | at the sequencing is executing and somewhere                                                                                                                                                                                                                               |  |  |  |

| 3   | seq_on       |     | IX. | between the st                                               | art of slot 1 and the end of slot 7. The bit                                                                                                                                                                                                                               |  |  |  |

|     |              |     |     | remains a 1 unt                                              | il slot 7 has completed at start-up or slot 1 has                                                                                                                                                                                                                          |  |  |  |

|     |              |     |     | finished at shute                                            | down, regardless of what slots are used.                                                                                                                                                                                                                                   |  |  |  |

|     |              |     |     | Indicates the slot number of SEQ at the moment:              |                                                                                                                                                                                                                                                                            |  |  |  |

|     |              |     |     | Register                                                     |                                                                                                                                                                                                                                                                            |  |  |  |

|     |              |     |     |                                                              | SEO Countor                                                                                                                                                                                                                                                                |  |  |  |

|     |              |     |     | Value                                                        | SEQ Counter                                                                                                                                                                                                                                                                |  |  |  |

|     |              |     |     | Value<br>000                                                 | SEQ Counter  Sequencing has completed or not started.                                                                                                                                                                                                                      |  |  |  |

|     |              |     |     | 7 011 01 0                                                   | ·                                                                                                                                                                                                                                                                          |  |  |  |

| 2:0 | sea cnt[2:0] | 000 | R   | 000                                                          | Sequencing has completed or not started.                                                                                                                                                                                                                                   |  |  |  |

| 2:0 | seq_cnt[2:0] | 000 | R   | 000                                                          | Sequencing has completed or not started.  Indicates was in slot 1 during register read                                                                                                                                                                                     |  |  |  |

| 2:0 | seq_cnt[2:0] | 000 | R   | 000<br>001<br>010                                            | Sequencing has completed or not started.  Indicates was in slot 1 during register read  Indicates was in slot 2 during register read                                                                                                                                       |  |  |  |

| 2:0 | seq_cnt[2:0] | 000 | R   | 000<br>001<br>010<br>011                                     | Sequencing has completed or not started.  Indicates was in slot 1 during register read  Indicates was in slot 2 during register read  Indicates was in slot 3 during register read                                                                                         |  |  |  |

| 2:0 | seq_cnt[2:0] | 000 | R   | 000<br>001<br>010<br>011<br>100                              | Sequencing has completed or not started.  Indicates was in slot 1 during register read  Indicates was in slot 2 during register read  Indicates was in slot 3 during register read  Indicates was in slot 4 during register read                                           |  |  |  |

| 2:0 | seq_cnt[2:0] | 000 | R   | 000<br>001<br>010<br>011<br>100<br>101                       | Sequencing has completed or not started.  Indicates was in slot 1 during register read Indicates was in slot 2 during register read Indicates was in slot 3 during register read Indicates was in slot 4 during register read Indicates was in slot 5 during register read |  |  |  |

### 0x0A LDSW\_RCB Register ----RCB Function Selection. Default = 0x00

This register enables the function blocking the current of load switch when the output voltage is higher than input.

| Bit | Name       | Default | Type  | Description                              |  |

|-----|------------|---------|-------|------------------------------------------|--|

| 7   | Rev.       | 0       | R     | Reserved                                 |  |

| 6   | Rev.       | 0       | R     | Reserved                                 |  |

| 5   | ldsw6_rcb  | 0       | R/W   | LDSW6 reverse current blocking function: |  |

| 3   | IdSW0_ICD  | U       | IN/VV | 0b:Disable 1b: Enable                    |  |

| 4   | ldsw5_rcb  | 0       | R/W   | LDSW5 reverse current blocking function: |  |

| 4   | IdSW3_ICD  | U       | 17/77 | 0b:Disable 1b: Enable                    |  |

| 3   | ldsw4_rcb  | 0       | R/W   | LDSW4 reverse current blocking function: |  |

| 3   | IdSW4_ICD  | U       | 17/77 | 0b:Disable 1b: Enable                    |  |

| 2   | ldsw3_rcb  | 0       | R/W   | LDSW3 reverse current blocking function: |  |

|     | IdSW3_ICD  | U       | 17/77 | 0b:Disable 1b: Enable                    |  |

| 1   | ldsw2_rcb  | 0       | R/W   | LDSW2 reverse current blocking function: |  |

| !   | IdSWZ_ICD  | U       | 17,77 | 0b:Disable 1b: Enable                    |  |

| 0   | ldsw1_rcb  | 0       | R/W   | LDSW1 reverse current blocking function: |  |

| U   | IUSW I_ICD | U       | 11/11 | 0b:Disable 1b: Enable                    |  |

### 0x0B LDSW\_STA Register ----LDSW Status Register. Default = 0x00

| Bit | Name      | Default | Type | Description        |

|-----|-----------|---------|------|--------------------|

| 7   | Rev.      | 0       | R    | Reserved           |

| 6   | Rev.      | 0       | R    | Reserved           |

|     |           |         |      | LDSW6 Status Bit:  |

| 5   | ldsw6_sta | 0       | R    | 0b:Turn off Status |

|     |           |         |      | 1b: Turn on Status |

|     |           |         |      | LDSW5 Status Bit:  |

| 4   | ldsw5_sta | 0       | R    | 0b:Turn off Status |

|     |           |         |      | 1b: Turn on Status |

|     |           |         |      | LDSW4 Status Bit:  |

| 3   | ldsw4_sta | 0       | R    | 0b:Turn off Status |

|     |           |         |      | 1b: Turn on Status |

|     |           |         |      | LDSW3 Status Bit:  |

| 2   | ldsw3_sta | 0       | R    | 0b:Turn off Status |

|     |           |         |      | 1b: Turn on Status |

|     |           |         |      | LDSW2 Status Bit:  |

| 1   | ldsw2_sta | 0       | R    | 0b:Turn off Status |

|     |           |         |      | 1b: Turn on Status |

|     |           |         |      | LDSW1 Status Bit:  |

| 0   | ldsw1_sta | 0       | R    | 0b:Turn off Status |

|     |           |         |      | 1b: Turn on Status |

### 0x69 SOFTRST\_CTR Register ----Software Reset Signal. Default = 0x00

Write B0H to this register will be produced a reset signal, this signal will reset all the registers to the default value.

| E  | 3it | Name        | Default | Type                                                               | Description                              |  |  |

|----|-----|-------------|---------|--------------------------------------------------------------------|------------------------------------------|--|--|

| ١, | 7:0 | 0           | R/W     | Write B0H to this register will reset all the registers to default |                                          |  |  |

| ′  | .0  | softrst_ctr | 00H     | K/VV                                                               | value, the read value always keep "00H". |  |  |

## **Absolute Maximum Ratings**

|                             | Items                        |                               |        |  |

|-----------------------------|------------------------------|-------------------------------|--------|--|

| POWER IN/                   | OUT Pins Voltage             | -0.3 to 6.0                   | \<br>\ |  |

| (IN1,IN2,IN34,IN56,OUT1,OUT | T2,OUT3.OUT4,OUT5,OUT6,VSYS) | -0.3 to 6.0                   | V      |  |

| Other                       | Pin Voltage                  | -0.3 to V <sub>SYS</sub> +0.3 | V      |  |

| Each Load Switch            | Maximum Load Current         | 2.0                           | А      |  |

| Maximum Po                  | ower Consumption             | 1200                          | mW     |  |

| Operating Jur               | nction Temperature           | -40 to 150                    | °C     |  |

| Storage                     | Temperature                  | -65 to 150                    | ۰C     |  |

| Lead Temperatu              | re (Soldering, 10 sec)       | 300                           | °C     |  |

| ESD                         | НМВ                          | ±2000                         |        |  |

| ESD                         | CDM                          | ±500                          | V      |  |

### **Electrical Characteristics**

Unless otherwise noted , Cvsys=1uF ,  $T_A$  = -40 °C ~85 °C. Typical values are at.  $T_A$ =25 °C

| Symbol             | Parameter                   | Test Conditions                                 | Min | Тур | Max | Unit |

|--------------------|-----------------------------|-------------------------------------------------|-----|-----|-----|------|

| Vvsys              | VSYS Voltage Range          |                                                 | 1.6 |     | 5.5 | V    |

| 1                  |                             | Active mode: V <sub>EN</sub> =V <sub>VSYS</sub> |     |     | 1   |      |

| IQ_ON              |                             | and Enable chip by I <sup>2</sup> C             |     |     | '   | μA   |

|                    | VSYS Current                | V <sub>EN</sub> =0V and                         |     |     |     |      |

| I <sub>Q_OFF</sub> |                             | Vaddr=Vscl=Vsda=0 or                            |     |     | 1   | μA   |

|                    |                             | Vaddr=Vscl=Vsda=Vvsys                           |     |     |     |      |

| R <sub>EN</sub>    | EN pin pull down Resistance |                                                 | 8   | 12  |     | ΜΩ   |

| I <sub>EN</sub>    | EN Leakage                  | V <sub>EN</sub> =5V                             |     |     | 0.6 | μA   |

| $V_{ENH}$          | EN Input Voltage High       |                                                 | 1.4 |     |     | V    |

| V <sub>ENH1</sub>  | EN Input Voltage High       | V <sub>SYS</sub> =1.8V                          | 1.1 |     |     | V    |

| V <sub>ENL</sub>   | EN Input Voltage Low        |                                                 |     |     | 0.3 | V    |

| V <sub>I2CH</sub>  | SCL/SDA Input Voltage High  |                                                 | 1.4 |     |     | V    |

| V <sub>I2CH1</sub> | SCL/SDA Input Voltage High  | V <sub>SYS</sub> =1.8V                          | 1.1 |     |     | V    |

| V <sub>I2CL</sub>  | SCL/SDA Input Voltage Low   |                                                 |     |     | 0.3 | V    |

| Vol                | SDA Logic Low Output        | 3mA Sink                                        |     |     | 0.4 | V    |

|                    |                             | EN=0 and                                        |     |     |     |      |

| l <sub>12C</sub>   | SCL/SDA Input Current       | $V_{SCL}=V_{SDA}=V_{VSYS}$ or                   |     | 0.1 |     | uA   |

|                    |                             | V <sub>SCL</sub> =V <sub>SDA</sub> =0           |     |     |     |      |

| FscL               | SCL Clock Frequency         |                                                 |     |     | 400 | kHz  |

## **Electrical Characteristics(Continued)**

Unless otherwise noted,  $V_{IN1}$ =  $V_{IN2}$ =  $V_{IN34}$ =  $V_{IN56}$ =1.2 to 5.5V,  $T_A$  = -40 to +85°C;

Typical values are at  $V_{\text{INX}}$  = 3.3V and  $T_{\text{A}}$  = 25°C.  $V_{\text{VSYS}}$ =1.6V to 5.5V

| Symbol                | Parameter                                   | Test Conditions                                                          | Min  | Тур | Max | Unit      |

|-----------------------|---------------------------------------------|--------------------------------------------------------------------------|------|-----|-----|-----------|

| Basic Opera           | ation                                       |                                                                          |      |     |     |           |

| V <sub>INX</sub>      | Input Voltage                               |                                                                          | 1.2  |     | 5.5 | V         |

|                       | Off Supply Current of                       | V <sub>EN</sub> =GND, V <sub>OUTX</sub> floating, V <sub>INX</sub> =5V   |      |     | 0.5 |           |

| $I_{QX(OFF)}$         | one channel LS                              | V <sub>EN</sub> =GND, V <sub>OUTX</sub> floating, V <sub>INX</sub> =3.3V |      |     | 0.5 | uA        |

|                       | T <sub>A</sub> =25°C                        | V <sub>EN</sub> =GND, V <sub>OUTX</sub> floating, V <sub>INX</sub> =1.8V |      |     | 0.5 |           |

|                       | Shutdown Current of                         | V <sub>EN</sub> = GND, V <sub>OUTX</sub> =0V, V <sub>INX</sub> =5V       |      |     | 0.5 |           |

| $I_{SD}$              | one channel LS                              | $V_{EN}$ = GND, $V_{OUTX}$ =0V, $V_{INX}$ =3.3V                          |      |     | 0.5 | μA        |

|                       | T <sub>A</sub> =25°C                        | V <sub>EN</sub> =GND, V <sub>OUTX</sub> =0V, V <sub>INX</sub> =1.8V      |      |     | 0.5 |           |

|                       | Quiescent Current of                        | $V_{EN}$ = $V_{VSYS}$ , $I_{OUTX}$ = $0$ mA, $V_{INX}$ = $5$ $V$         |      |     | 0.5 |           |

| $I_Q$                 | one channel LS                              | $V_{EN} = V_{VSYS}$ , $I_{OUTX}=0$ mA, $V_{INX}=3.3$ V                   |      |     | 0.5 | μA        |

|                       | T <sub>A</sub> =25°C (RCB off)              | $V_{EN} = V_{VSYS}$ , $I_{OUTX}=0$ mA, $V_{INX}=1.8$ V                   |      |     | 0.5 |           |

|                       | Quiescent Current of                        | $V_{EN}$ = $V_{VSYS}$ , $I_{OUTX}$ = $0$ mA, $V_{INX}$ = $5$ $V$         |      | 1.5 | 4   |           |

| $I_{Q_R}$             | one channel LS                              | $V_{EN} = V_{VSYS}$ , $I_{OUTX}=0$ mA, $V_{INX}=3.3$ V                   |      | 0.9 | 2.5 | μΑ        |

|                       | T <sub>A</sub> =25°C(RCB on)                | $V_{EN} = V_{VSYS}$ , $I_{OUTX}=0$ mA, $V_{INX}=1.8$ V 0.3               |      | 0.3 | 0.8 |           |

|                       | On-Resistance                               | V <sub>INX</sub> =5V, I <sub>OUTX</sub> =200mA                           |      | 52  | 70  |           |

| Ron                   | T <sub>A</sub> =25°C                        | V <sub>INX</sub> =3.3V, I <sub>OUTX</sub> =200mA                         |      | 66  | 85  | $m\Omega$ |

|                       | TA=25°C                                     | V <sub>INX</sub> =1.8V, I <sub>OUTX</sub> =200mA                         |      | 120 | 150 |           |

| $R_{\mathtt{PD}}$     | OUT pin Discharge                           | $V_{INX} = 3.3V$ , $EN = 0V$ ,                                           |      | 66  | 100 | Ω         |

| MPD                   | Resistance (default)                        | $V_{OUTX}=1V$ , $T_A=25$ °C                                              |      | 00  | 100 | 12        |

| True Revers           | se Current Blocking                         |                                                                          |      |     |     |           |

| V <sub>T_RCB</sub>    | RCB Protection                              | Vout - Vinx                                                              |      | 60  |     | mV        |

| A I_KCR               | Trip Point                                  | VOUI - VINX                                                              |      | 00  |     | IIIV      |

| $V_{R\_RCB}$          | RCB Protection                              | Vinx - Vout                                                              |      | 65  |     | mV        |

| V K_KCD               | Release Trip Point                          | VIIIX VOOT                                                               | V001 |     |     | 111 V     |

|                       | RCB Hysteresis                              |                                                                          |      | 125 |     | mV        |

| I <sub>SD_OUT</sub>   | VOUT Shutdown                               | LSW off, V <sub>OUT</sub> =5.0V, V <sub>IN</sub> =Short to GND           |      | 1.4 |     | uA        |

| .00_001               | Current                                     | 2011 011, 1001 0101, 1111 0110110 0110                                   |      |     |     |           |

|                       | RCB Response                                |                                                                          |      |     |     |           |

| $T_{RCB}_{ON}$        | Time when                                   | V <sub>OUT</sub> - V <sub>IN</sub> =200mV, V <sub>ON</sub> =High         |      | 3   |     | uS        |

|                       | Device ON <sup>(1)</sup>                    |                                                                          |      |     |     |           |

| T <sub>RCB_OFF</sub>  | RCB Response Time                           | VIN - VOUT =200mV, VON=High                                              |      | 4   |     | uS        |

|                       | Device OFF <sup>(1)</sup>                   |                                                                          |      |     |     |           |

|                       |                                             | ions Below(default mode)                                                 | 1    |     | 1   | <u> </u>  |

| t <sub>DON</sub>      | Turn-On Delay <sup>(1,2)</sup>              | $V_{INX} = 3.3V$ , $R_L = 150\Omega$ ,                                   |      | 270 |     | _         |

| <b>t</b> <sub>R</sub> | Vout Rise Time <sup>(1.2)</sup>             | C <sub>L</sub> =0.1µF,T <sub>A</sub> =25℃                                |      | 340 |     | us        |

| tdon                  | Turn-On Delay (1,2)                         | $V_{INX} = 3.3V$ , $R_L = 500\Omega$ ,                                   |      | 250 |     | _         |

| t <sub>R</sub>        | V <sub>OUT</sub> Rise Time <sup>(1.2)</sup> | C∟=0.1µF,T <sub>A</sub> =25°C                                            |      | 320 |     |           |

| t <sub>DOFF</sub> | Turn-Off Delay (1,2)                        | V <sub>INX</sub> =3.3V, R <sub>L</sub> =150Ω, | 0.8  |    |

|-------------------|---------------------------------------------|-----------------------------------------------|------|----|

| $t_{F}$           | V <sub>OUT</sub> Fall Time <sup>(1,2)</sup> | C∟=0.1µF,T <sub>A</sub> =25°C                 | 10.5 |    |

| t <sub>DOFF</sub> | Turn-Off Delay (1,2)                        | $V_{INX}$ =3.3V, $R_L$ =500 $\Omega$ ,        | 1.1  | us |

| t <sub>F</sub>    | V <sub>OUT</sub> Fall Time <sup>(1,2)</sup> | $C_L$ =0.1 $\mu$ F, $T_A$ =25 $^{\circ}$ C    | 14   |    |

| t <sub>DON</sub>  | Turn-On Delay <sup>(1,2)</sup>              | $V_{INX}$ =1.8V, $R_L$ =150 $\Omega$ ,        | 560  |    |

| $t_R$             | V <sub>OUT</sub> Rise Time <sup>(1.2)</sup> | $C_L$ =0.1 $\mu$ F, $T_A$ =25 $^{\circ}$ C    | 560  |    |

| tDOFF             | Turn-Off Delay (1,2)                        | $V_{INX}$ =1.8 $V$ , $R_L$ =150 $\Omega$ ,    | 0.9  | us |

| t₅                | Vout Fall Time(1,2)                         | $C_L$ =0.1 $\mu$ F, $T_A$ =25 $^{\circ}$ C    | 12.6 |    |

#### Notes:

- 1. This parameter is guaranteed by design and characterization; not production tested.

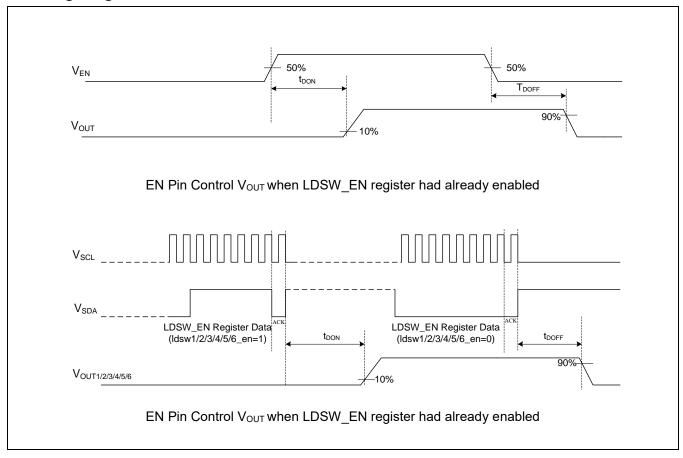

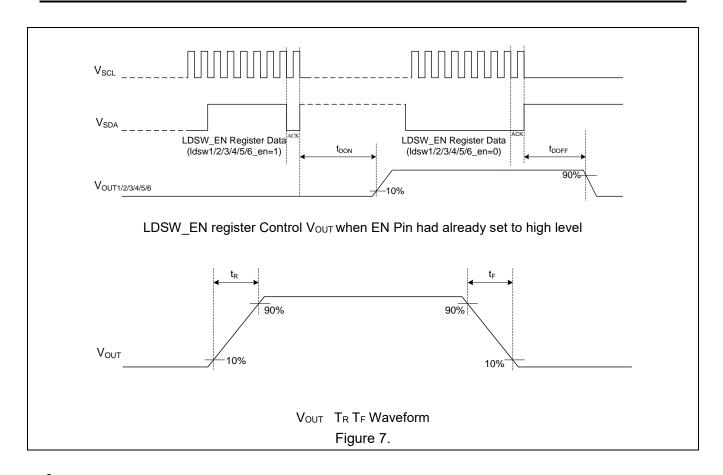

- 2.  $t_{DON}/t_{DOFF}/t_R/t_F$  are defined in Figure 3.

### **Timing Diagram**

## I<sup>2</sup>C Mode Timing

| Symbol              | Parameter                                         | Min                     | Тур | Max | Unit |

|---------------------|---------------------------------------------------|-------------------------|-----|-----|------|

| F <sub>SCL</sub>    | SCL Clock Frequency                               | 0                       | -   | 400 | KHz  |

| t <sub>BUF</sub>    | Bus Free Time Between a STOP and START  Condition | 1.3                     | -   | -   | μs   |

| t <sub>HD:STA</sub> | Hold Time(Repeated) START Condition               | 0.6                     | -   | -   | μs   |

| $t_{LOW}$           | Low Period of SCL Clock                           | 1.3                     | -   | -   | μs   |

| t <sub>HIGH</sub>   | HIGH Period of SCL Clock                          | 0.6                     | -   | -   | μs   |

| t <sub>SU:STA</sub> | Setup Time for a Repeated START Condition         | 0.6                     | -   | -   | μs   |

| t <sub>HD:DAT</sub> | Data Hold Time                                    | -                       | -   | 0.9 | μs   |

| t <sub>SU:DAT</sub> | Data Setup Time                                   | 100                     | -   | -   | ns   |

| t <sub>R</sub>      | Data Hold Time2                                   | 20+0.1Cb <sup>(3)</sup> | -   | 300 | ns   |

| $t_{F}$             | Data Hold Time2                                   | 20+0.1Cb <sup>(3)</sup> | -   | 300 | ns   |

| t <sub>SU:STO</sub> | Setup Time for STOP Condition                     | 0.6                     | -   | -   | μs   |

19

Note3: Cb=total capacitance of one bus line in PF.

### I<sup>2</sup>C mode Timing Diagram

## **Application Circuits**

## **Package Dimension**

| SYMBOL | MIN   | NOM      | MAX   |  |  |  |  |

|--------|-------|----------|-------|--|--|--|--|

| Α      | 0.430 | 0.480    | 0.530 |  |  |  |  |

| A1     | 0.110 | 0.130    | 0.150 |  |  |  |  |

| A2     | 0.320 | 0.350    | 0.380 |  |  |  |  |

| b      | 0.140 | 0.160    | 0.180 |  |  |  |  |

| D      | 1.520 | 1.540    | 1.560 |  |  |  |  |

| Е      | 1.520 | 1.540    | 1.560 |  |  |  |  |

| е      |       | 0.350BSC |       |  |  |  |  |

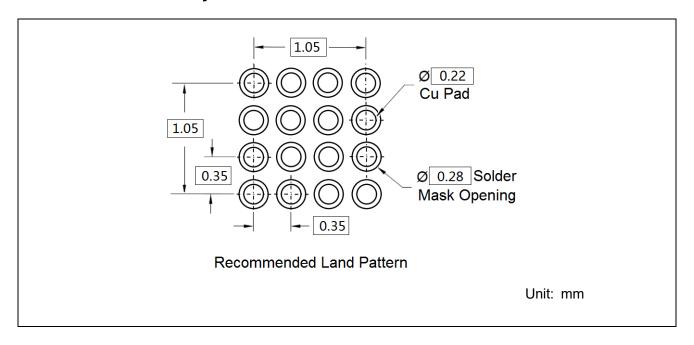

## **Recommended PCB Layout**

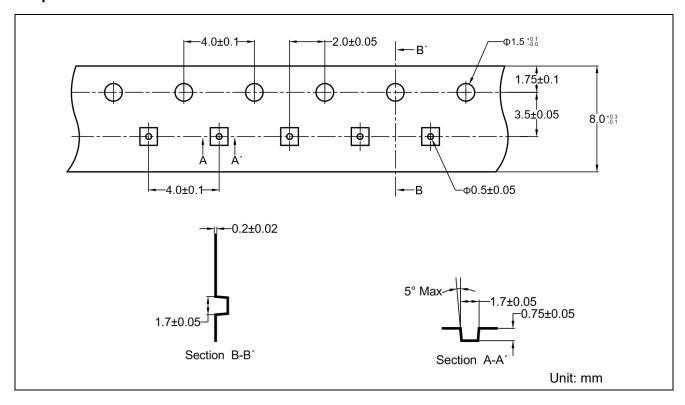

### **Tape Information**

## **Revision History and Checking Table**

| Version | Date      | Revision Item      | Modifier | Function & Spec<br>Checking | Package & Tape<br>Checking |

|---------|-----------|--------------------|----------|-----------------------------|----------------------------|

| 1.0     | 2021-5-31 | Initial Version    | Wuxj     | Wuxj                        | Liujy                      |

| 1.1     | 2021-11-4 | Add VIH@VSYS =1.8V | Wuxj     | Wuxj                        | Liujy                      |

| 1.2     | 2022-8-21 | Update Typeset     | ShiB     | Wuxj                        | Liujy                      |