# 80mΩ Adjustable Current Limited Power Switches

### **General Description**

The ET2016A are current limited P-channel MOSFET power switch designed for high-side load switching applications. This switch operates with inputs ranging from 2.5V to 5.5V, making it ideal for both 3.3V and 5V systems. An integrated current-limiting circuit protects the input supply against large currents which may cause the supply to fall out of regulation. The ET2016A is also protected from thermal overload which limits power dissipation and junction temperatures. It can be used to control loads that require from 0.4A to 2A. Current limit threshold is programmed with a resistor from SET to ground. The quiescent supply current in active mode is only 25µA. In shutdown mode, the supply current decreases to less than 1µA.

The ET2016A is available in Pb-free packages and is specified over the -40°C to +85°C ambient temperature range.

#### **Features**

Input Voltage Range: 2.5V to 5.5V

Programmable Current Limit

Reverse Current Blocking

Short-Circuit Response: 2us

Very Low Quiescent Current: 25µA (Typ)

- 1µA Max Shutdown Supply Current

- Under-Voltage Lockout

- Thermal Shutdown

- 4kV ESD Rating

- Part No. and Package

| Part No. | Package | Packing Option         | MSL |

|----------|---------|------------------------|-----|

| ET2016A  | SOT23-5 | Tape and Reel, 3K/Reel | 1   |

1

#### **Application**

- Laptop/Desktop Computers and NootBooks

- Smart Phones and PDAs

- LCD TVs and Monitors

- Set-Top-Boxes

- Printers

- Portable Media Players and MIDs

- USB Keyboards

- USB Hard Disk Drives

- USB Memory Drives

- USB Hubs

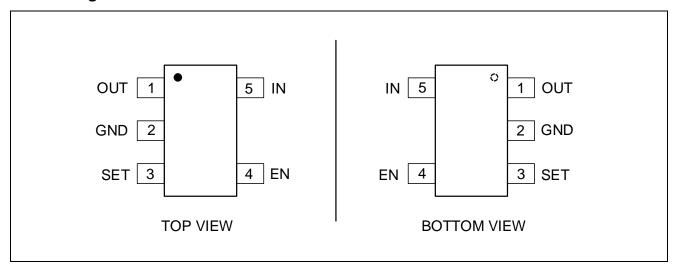

## **Pin Configuration**

### **Pin Function**

| Pin | Name | Description                                                         |

|-----|------|---------------------------------------------------------------------|

| 1   | OUT  | Power output.                                                       |

| 2   | GND  | Ground pin.                                                         |

| 3   | SET  | Current limit programming pin, with a resistor from ISET to ground. |

| 4   | EN   | Enable input, high enable.                                          |

| 5   | IN   | Power supply input.                                                 |

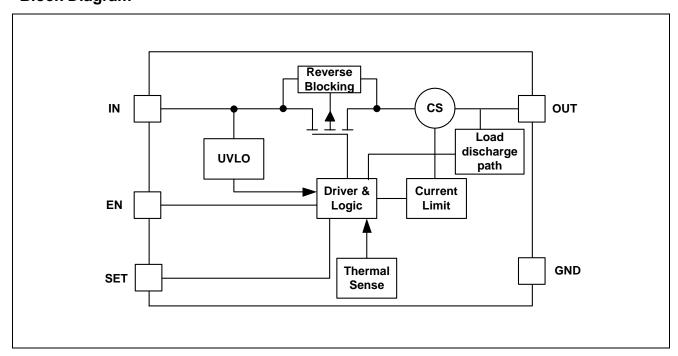

## **Block Diagram**

#### Operation

ET2016A is an integrated power switch with a low Rdson P-channel MOSFET, internal gate rive circuit, programmable current limiting. When the ET2016A turns on, it can deliver up to 2A continuous current to load. When the device is active, if there is no load, the device only consumes 25uA supply current, which makes the device suitable for battery powered applications.

#### **Power Supply Considerations**

A 0.01µF to 0.1µF ceramic bypass capacitor between IN and GND, close to the device, is recommended.

Placing a high-value electrolytic capacitor on the output pin(s) is recommended when the output load is heavy. This precaution reduces power-supply transients that may cause ringing on the input and minimize the input voltage droops. Additionally, bypassing the output with a 0.01µF to 0.1µF ceramic capacitor improves the immunity of the device to short-circuit transients.

#### **Power Dissipation and Junction Temperature**

The low on-resistance on the P-channel MOSFET allows the small surface-mount packages to pass large currents. It is good design practice to check power dissipation and junction temperature for each application. Begin by determining the  $R_{DS(ON)}$  of the P-channel MOSFET relative to the input voltage and operating temperature. Using the highest operating ambient temperature of interest and  $R_{DS(ON)}$ , the power dissipation per switch can be calculated by:

$$P_D = R_{DS(ON)} \times I_{OUT}^2 \tag{1}$$

Finally, calculate the junction temperature:

$$T_J = P_D \times R_{\theta JA} + T_A \tag{2}$$

Where:

T<sub>A</sub>= Ambient temperature

$R_{\theta JA}$  = Thermal resistance

$P_D$  = Total power dissipation

Compare the calculated junction temperature with the maximum junction temperature which is 150°C. If they are within degrees, either the maximum load current needs to be reduced or another package option will be required.

#### **Over Current**

A sense FET is employed to check for over-current conditions. When an over-current condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. ET2016A will limit the current until the overload condition is removed or the device begins to thermal cycle.

Three possible overload conditions can occur. In the first condition, the output has been shorted before the device is enabled or before VIN has been applied. The ET2016A senses the short and immediately switches into a constant-current output.

In the second condition, a short or an overload occurs while the device is enabled. At the instant the overload

#### ET2016A

occurs, high currents may flow for a short period of time before the current-limit circuit can react .

After the current-limit circuit reached the over-current trip threshold, the device switches into constant-current mode.

In the third condition, the load has been gradually increased beyond the recommended operating current. The current is permitted to rise until the current-limit threshold is reached or until the thermal limit of the device is exceeded. The ET2016A is capable of delivering current up to the current-limit threshold without damaging the device. Once the threshold has been reached, the device switches into its constant-current mode.

#### **Thermal Protection**

Thermal protection prevents damage to the IC when heavy-overload or short-circuit faults are present for extended periods of time. The ET2016A implements a thermal sensing to monitor the operating junction temperature of the power distribution switch. In an over-current or short-circuit condition, the junction temperature rises due to excessive power dissipation.

Once the die temperature rises to approximately  $155^{\circ}$ C due to over-current conditions, the internal thermal sense circuitry turns the power switch off, thus preventing the power switch from damage. Hysteresis is built into the thermal sense circuit, and after the device has cooled approximately  $25^{\circ}$ C, the switch turns back on. The switch continues to cycle in this manner until the load fault or input power is removed.

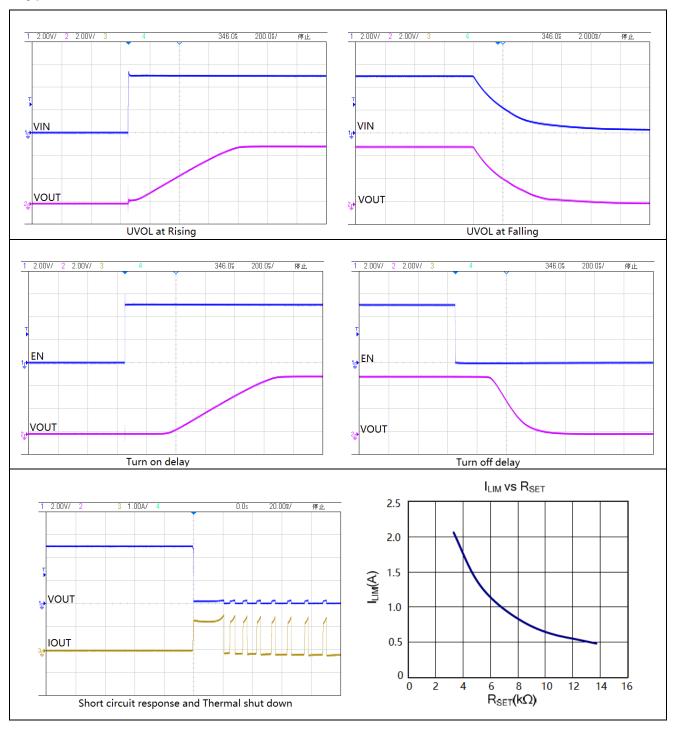

#### **Current Limiting Setting**

Current limit is programmable to protect the power source from over current and short circuit conditions. Connect a resistor RSET from SET pin to GND to program the current limit:

$$I_{LIM}(A) = 6800/R_{SET} (\Omega)$$

(3)

The minimum current limit is 0.4A. Current limit beyond 2A is not recommended. The formula is for reference only, please refer to the actual test flow limiting curve.

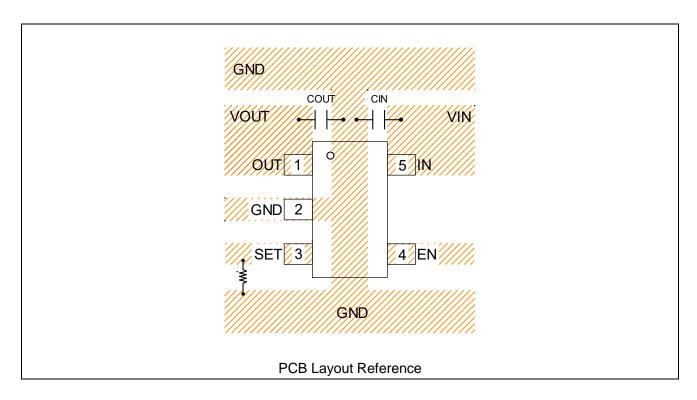

#### **PCB Layout Guide**

PCB layout is very important to achieve stable operation. It is highly recommended to duplicate EVB layout for optimum performance. If change is necessary, please follow these guidelines for reference.

- 1) Keep the path of current short and minimize the loop area formed by Input and output capacitor.

- 2) Output capacitor and IC must be on the same side, The distance of OUT pin and output capacitor <3mm is recommended.

- 3) Bypass ceramic capacitors are suggested to be put close to the IN Pin.

- 4) Connect IN, OUT, and especially GND respectively to a large copper area to cool the chip to improve thermal performance and long-term reliability.

### **Absolute Maximum Ratings**

| Parameter                                        | Rating                        | Unit |  |

|--------------------------------------------------|-------------------------------|------|--|

| IN, EN,SET Voltage                               | -0.3 to 6.0                   | V    |  |

| OUT Voltage                                      | -0.3 to V <sub>IN</sub> + 0.3 | V    |  |

| OUT Current                                      | Adjustable Current            | Α    |  |

| Power Dissipation (T <sub>A</sub> = 25°C)        | 500                           | mW   |  |

| Package Thermal Resistance (θ <sub>JA</sub> )    | 250                           | °C/W |  |

| Operating Junction Temperature (T <sub>J</sub> ) | -40 to 150                    | °C   |  |

| Storage Temperature (T <sub>STG</sub> )          | -65 to 150                    | °C   |  |

| Lead Temperature (Soldering, 10 sec)             | 300                           | °C   |  |

**Note:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

# ET2016A

## **Electrical Characteristics**

( $V_{IN}$  = +5.0V,  $T_A$  = -40°C to 85°C, typical values at  $T_A$ =25°C, unless otherwise stated)

| Symbol              | Parameter                              | Test Conditions                                                        | Min  | Тур  | Max  | Unit |

|---------------------|----------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| Vin                 | Input Voltage Range                    |                                                                        | 2.5  |      | 5.5  | V    |

| V <sub>UVLO</sub>   | Input UVLO Voltage                     |                                                                        | 1.4  | 1.8  | 2.3  | V    |

| Vuvlo_HYS           | UVLO Hysteresis                        |                                                                        |      | 0.25 |      | ٧    |

| Ishdn               | Input Shutdown Quiescent Current       | Disabled, OUT floating or shorted to ground                            |      | 0.1  | 1    | uA   |

| IQ                  | Input Quiescent Current                | Enabled, V <sub>EN</sub> =V <sub>IN</sub> , I <sub>OUT</sub> = 0A      | 10   | 25   | 60   | uA   |

| R <sub>DS(ON)</sub> | Switch on-resistance                   | V <sub>IN</sub> =5V, I <sub>OUT</sub> =0.6A                            | 60   | 80   | 120  | mΩ   |

|                     |                                        | V <sub>IN</sub> =5V, V <sub>OUT</sub> =4.5V, R <sub>SET</sub> =6.8K    | 0.75 | 1    | 1.25 | Α    |

| I <sub>LMT</sub>    | Current Limit                          | V <sub>IN</sub> =5V, V <sub>OUT</sub> =4.5V, R <sub>SET</sub> =5.6K    | 0.91 | 1.21 | 1.51 | Α    |

|                     |                                        | Min Current Limit                                                      |      | 0.4  |      | Α    |

| VIL                 | EN Input Logic Low Voltage             |                                                                        |      |      | 0.8  | V    |

| VIH                 | EN Input Logic High Voltage            |                                                                        | 1.7  |      |      | V    |

| I <sub>SINK</sub>   | EN Input leakage                       | $V_{EN} = 5V$                                                          |      | 0.01 | 1    | uA   |

| t <sub>ON</sub>     | Output Turn-on Delay Time              | $V_{IN}$ =5V, $C_L$ =1uF, $R_L$ =100 $\Omega$                          | 0.2  | 0.6  | 1.0  | ms   |

| t <sub>R</sub>      | Output Turn-on Rise Time               | $V_{IN}$ =5V, $C_L$ =1uF, $R_L$ =100 $\Omega$                          | 0.2  | 0.5  | 0.8  | ms   |

| toff                | Output Turn-off Delay Time             | $V_{IN}$ =5V, $C_L$ =1uF, $R_L$ =100 $\Omega$                          | 0.1  | 0.3  | 0.5  | ms   |

| t <sub>F</sub>      | Output Turn-off Fall Time              | $V_{IN}$ =5V, $C_L$ =1uF, $R_L$ =100 $\Omega$                          | 50   | 120  | 200  | us   |

| R <sub>DIS</sub>    | Output Discharge FET R <sub>DSON</sub> | V <sub>IN</sub> = 5V, V <sub>EN</sub> =0V, V <sub>OUT</sub> =5V        | 200  | 400  | 800  | Ω    |

| I <sub>REV</sub>    | Reverse leakage current                | V <sub>OUT</sub> = 5V , V <sub>IN</sub> = 0V measure I <sub>VOUT</sub> | 0.1  | 1    | 3    | uA   |

| T <sub>SHDN</sub>   | Thermal shutdown threshold             | V <sub>IN</sub> = 5V                                                   | 140  | 155  | 165  | °C   |

| T <sub>HYS</sub>    | Thermal shutdown hysteresis            | V <sub>IN</sub> = 5V                                                   |      | 25   |      | °C   |

## **Typical Performance Characteristics**

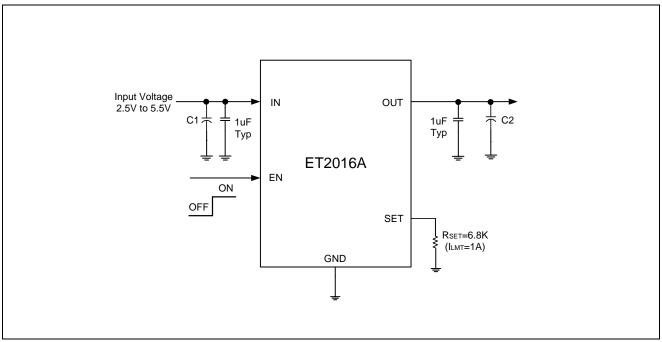

## **Application Circuits**

Note: Tantalum or Aluminum Electrolytic capacitors (C1 and C2) may be required for USB applications.

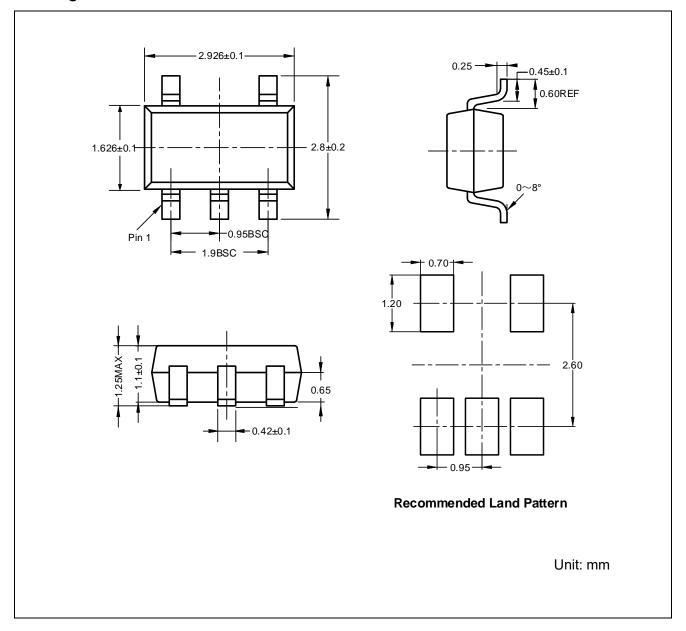

# Package Dimension

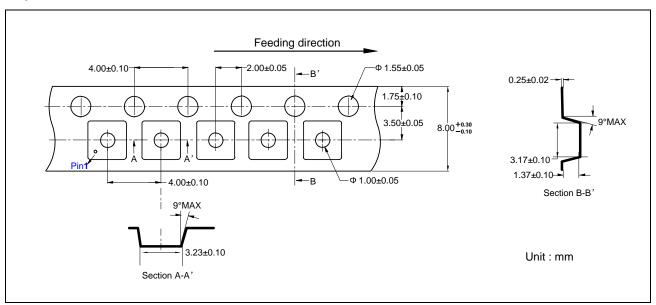

## **Tape Information**

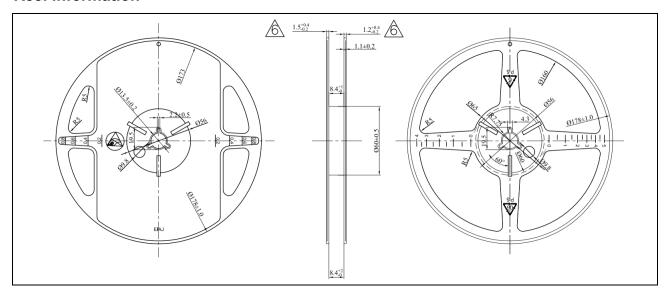

### **Reel Information**

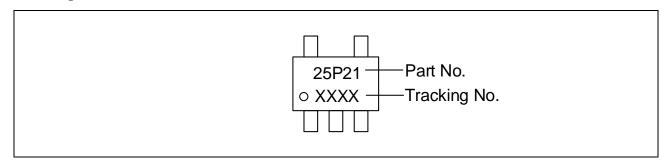

## Marking

# ET2016A

# **Revision History and Checking Table**

| Version | Date       | Revision Item                 | Modifier   | Function & Spec Checking | Package & Tape<br>Checking |

|---------|------------|-------------------------------|------------|--------------------------|----------------------------|

| 1.0     | 2016-04-22 | Original version              | Liu Yi Guo | Liu Yi Guo               | Zhujl                      |

| 1.1     | 2020-5-8   | Update form                   | Shibo      | Shibo                    | Zhujl                      |

| 1.2     | 2021-4-7   | Update EC table and title     | Liu Yi Guo | Liu Yi Guo               | Zhujl                      |

| 1.3     | 2021-05-17 | Add RSET=5.6k ILIMIT value    | Liu Yi Guo | Liu Yi Guo               | Zhujl                      |

| 1.4     | 2022-08-28 | Update format                 | Wu He Song | Wu Hesong                | Zhujl                      |

| 1.5     | 2025-11-06 | Add Tape and Reel Information | Wu He Song | Wu Hesong                | Liujy                      |

|         |            |                               |            |                          |                            |